Bulldozer (microarquitectura) - Bulldozer (microarchitecture)

| Información general | |

|---|---|

| Lanzado | Finales de 2011 |

| Interrumpido | Regalo |

| Fabricante (s) común (es) | |

| Arquitectura y clasificación | |

| Min. tamaño de la característica | 32 millas náuticas |

| Conjunto de instrucciones | x86-64 |

| Especificaciones físicas | |

| Enchufe (s) | |

| Productos, modelos, variantes | |

| Nombre (s) principal | |

| Historia | |

| Predecesor | Familia 10h (K10) |

| Sucesor | Piledriver - Familia 15h (2.a generación) |

La AMD Bulldozer Family 15h es una microarquitectura de microprocesador para la línea de procesadores FX y Opteron , desarrollada por AMD para los mercados de escritorio y servidores. Bulldozer es el nombre en clave de esta familia de microarquitecturas. Fue lanzado el 12 de octubre de 2011 como sucesor de la microarquitectura K10 .

Bulldozer está diseñado desde cero, no es un desarrollo de procesadores anteriores. El núcleo está dirigido específicamente a productos informáticos con TDP de 10 a 125 vatios . AMD afirma mejoras dramáticas en la eficiencia del rendimiento por vatio en aplicaciones de computación de alto rendimiento (HPC) con núcleos Bulldozer.

Los núcleos Bulldozer admiten la mayoría de los conjuntos de instrucciones implementados por los procesadores Intel ( Sandy Bridge ) disponibles en su introducción (incluidos SSE4.1 , SSE4.2 , AES , CLMUL y AVX ), así como los nuevos conjuntos de instrucciones propuestos por AMD; ABM , XOP , FMA4 y F16C . Solo Bulldozer GEN4 ( Excavator ) admite conjuntos de instrucciones AVX2 .

Visión general

Según AMD, las CPU basadas en Bulldozer se basan en la tecnología de proceso Silicon on insulator (SOI) de 32 nm de GlobalFoundries y reutilizan el enfoque de DEC para el rendimiento de la computadora multitarea con los argumentos de que, según las notas de prensa, "equilibra la computadora dedicada y compartida recursos para proporcionar un diseño altamente compacto y de gran cantidad de unidades que se replica fácilmente en un chip para escalar el rendimiento ". En otras palabras, al eliminar algunos de los elementos "redundantes" que se introducen naturalmente en los diseños multinúcleo, AMD ha esperado aprovechar mejor sus capacidades de hardware, utilizando menos energía.

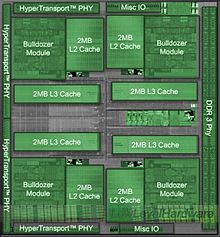

Las implementaciones basadas en bulldozer construidas en SOI de 32 nm con HKMG llegaron en octubre de 2011 tanto para servidores como para computadoras de escritorio. El segmento de servidores incluía el procesador Opteron de doble chip (16 núcleos) con nombre en código Interlagos (para Socket G34 ) y de un solo chip (4, 6 u 8 núcleos) Valencia (para Socket C32 ), mientras que el Zambezi (4, 6 y 8 núcleos) escritorios específicos en Socket AM3 + .

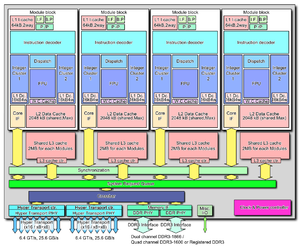

Bulldozer es el primer rediseño importante de la arquitectura del procesador de AMD desde 2003, cuando la empresa lanzó sus procesadores K8, y también cuenta con dos FPU de 128 bits con capacidad FMA que se pueden combinar en una FPU de 256 bits. Este diseño está acompañado por dos grupos de enteros, cada uno con 4 canalizaciones (la etapa de recuperación / decodificación es compartida). Bulldozer también introdujo la caché L2 compartida en la nueva arquitectura. AMD llama a este diseño un "Módulo". Un diseño de procesador de 16 núcleos incluiría ocho de estos "módulos", pero el sistema operativo reconocerá cada "módulo" como dos núcleos lógicos.

La arquitectura modular consta de caché L2 compartida multiproceso y FlexFPU, que utiliza multiproceso simultáneo . Cada núcleo entero físico, dos por módulo, es de un solo subproceso, en contraste con el Hyperthreading de Intel , donde dos subprocesos virtuales simultáneos comparten los recursos de un solo núcleo físico.

Arquitectura

Núcleo de la excavadora

Bulldozer hizo uso de "Clustered Multithreading" (CMT), una técnica en la que algunas partes del procesador se comparten entre dos subprocesos y algunas partes son únicas para cada subproceso. Los ejemplos anteriores de este enfoque de subprocesos múltiples no convencionales se remontan a la CPU UltraSPARC T1 de Sun Microsystems de 2005 . En términos de complejidad y funcionalidad del hardware, un módulo Bulldozer CMT equivale a un procesador de doble núcleo en sus capacidades de cálculo de números enteros, y a un procesador de un solo núcleo o un doble núcleo para discapacitados en términos de potencia computacional de punto flotante, según sobre si el código está saturado en instrucciones de punto flotante en ambos subprocesos que se ejecutan en el mismo módulo CMT, y si la FPU está realizando operaciones de punto flotante de 128 o 256 bits. La razón de esto es que por cada dos núcleos enteros, es decir, dentro del mismo módulo, hay una única unidad de coma flotante que consta de un par de unidades de ejecución FMAC de 128 bits .

CMT es de alguna manera una filosofía de diseño más simple pero similar a SMT ; ambos diseños intentan utilizar las unidades de ejecución de manera eficiente; en cualquier método, cuando dos subprocesos compiten por algunas canalizaciones de ejecución, hay una pérdida de rendimiento en uno o más de los subprocesos. Debido a los núcleos enteros dedicados, los módulos de la familia Bulldozer funcionaron aproximadamente como un procesador de doble núcleo y doble subproceso durante secciones de código que eran enteramente enteras o una combinación de cálculos de enteros y de punto flotante; sin embargo, debido al uso SMT de las canalizaciones de punto flotante compartidas, el módulo funcionaría de manera similar a un procesador SMT de un solo núcleo y doble subproceso (SMT2) para un par de subprocesos saturados con instrucciones de punto flotante. (Estas dos últimas comparaciones suponen que el procesador posee un núcleo de ejecución igualmente amplio y capaz, en cuanto a números enteros y en coma flotante, respectivamente).

Tanto CMT como SMT tienen la máxima eficacia al ejecutar código entero y de punto flotante en un par de subprocesos. CMT se mantiene en su máxima eficacia mientras trabaja en un par de subprocesos que constan de código entero, mientras que en SMT, uno o ambos subprocesos tendrán un rendimiento inferior debido a la competencia por las unidades de ejecución de enteros. La desventaja de CMT es un mayor número de unidades de ejecución de enteros inactivas en un caso de un solo subproceso. En el caso de un solo subproceso, CMT está limitado a utilizar como máximo la mitad de las unidades de ejecución de enteros en su módulo, mientras que SMT no impone tal límite. Un gran núcleo SMT con circuitos enteros tan ancho y rápido como dos núcleos CMT podría, en teoría, tener momentáneamente hasta el doble de un rendimiento entero en un caso de un solo hilo. (De manera más realista para el código general en su conjunto, la regla de Pollack estima un factor de aceleración o aproximadamente un 40% de aumento en el rendimiento).

Los procesadores CMT y un procesador SMT típico son similares en su uso compartido eficiente de la caché L2 entre un par de subprocesos.

- Un módulo consiste en un acoplamiento de dos núcleos de procesamiento fuera de servicio x86 "convencionales". El núcleo de procesamiento comparte las primeras etapas de la canalización (por ejemplo , L1i , recuperación, decodificación), las FPU y la caché L2 con el resto del módulo.

- Cada módulo tiene los siguientes recursos de hardware independientes:

- 16 KB de 4 vías de L1d (vía predicha) por núcleo y 64 KB de 2 vías de L1i por módulo, una vía para cada uno de los dos núcleos

- 2 MB de caché L2 por módulo (compartido entre los dos núcleos enteros)

- Write Coalescing Cache es una caché especial que forma parte de la caché L2 en la microarquitectura Bulldozer. Los almacenes de ambos cachés L1D en el módulo pasan por el WCC, donde se almacenan en búfer y se fusionan. La tarea del WCC es reducir el número de escrituras en la caché L2.

- Dos núcleos enteros dedicados

- - cada uno incluye dos ALU y dos AGU que son capaces de un total de cuatro operaciones aritméticas y de memoria independientes por reloj y por núcleo

- - la duplicación de programadores de enteros y canalizaciones de ejecución ofrece hardware dedicado a cada uno de los dos subprocesos que duplican el rendimiento para cargas de enteros de subprocesos múltiples

- - el segundo núcleo entero en el módulo aumenta la matriz del módulo Bulldozer en aproximadamente un 12%, que a nivel de chip agrega aproximadamente un 5% del espacio total de la matriz

- Dos canalizaciones de coma flotante FMAC simétricas de 128 bits (capacidad fusionada de multiplicación y adición ) por módulo que se pueden unificar en una unidad grande de 256 bits de ancho si uno de los núcleos enteros envía instrucciones AVX y dos simétricas con capacidad x87 / MMX / SSE FPP para compatibilidad con versiones anteriores de software no optimizado SSE2. Cada unidad FMAC también puede realizar operaciones de división y raíz cuadrada con latencia variable.

- Todos los módulos presentes comparten la caché L3, así como un subsistema de memoria de doble canal avanzado (IMC - Integrated Memory Controller).

- Un módulo tiene 213 millones de transistores en un área de 30,9 mm² (incluida la caché L2 compartida de 2 MB) en una matriz Orochi.

- La profundidad de la tubería de Bulldozer (así como Piledriver y Steamroller) es de 20 ciclos, en comparación con los 12 ciclos del predecesor del núcleo K10.

La tubería más larga permitió a la familia de procesadores Bulldozer lograr una frecuencia de reloj mucho más alta en comparación con sus predecesores K10. Si bien esto aumentó las frecuencias y el rendimiento, la tubería más larga también aumentó las latencias y aumentó las penalizaciones por predicción errónea de rama .

- El ancho del núcleo entero de la Bulldozer, cuatro (2 ALU, 2 AGU), es algo menor que el ancho del núcleo K10, seis (3 ALU, 3 AGU). Bobcat y Jaguar también utilizaron un núcleo entero de cuatro anchos, pero con unidades de ejecución más ligeras: 1 ALU, 1 ALU simple, 1 carga AGU, 1 tienda AGU.

Los anchos de emisión (y ejecuciones máximas de instrucciones por ciclo) de un núcleo Jaguar, K10 y Bulldozer son 2, 3 y 4 respectivamente. Esto convirtió a la Bulldozer en un diseño más superescalar en comparación con Jaguar / Bobcat. Sin embargo, debido al núcleo algo más ancho de K10 (además de la falta de refinamientos y optimizaciones en un diseño de primera generación), la arquitectura Bulldozer generalmente se desempeñó con un IPC algo más bajo en comparación con sus predecesores K10. No fue hasta los refinamientos realizados en Piledriver y Steamroller, que el IPC de la familia Bulldozer claramente comenzó a superar al de los procesadores K10 como Phenom II.

Predictor de rama

- Búfer de destino de bifurcación de dos niveles (BTB)

- Predictor híbrido para condicionales

- Predictor indirecto

Extensiones de conjuntos de instrucciones

- Compatibilidad con el conjunto de instrucciones Advanced Vector Extensions ( AVX ) de Intel , que admite operaciones de punto flotante de 256 bits y SSE4.1 , SSE4.2 , AES , CLMUL , así como futuros conjuntos de instrucciones de 128 bits propuestos por AMD ( XOP , FMA4 , y F16C ), que tienen la misma funcionalidad que el conjunto de instrucciones SSE5 propuesto anteriormente por AMD, pero con compatibilidad con el esquema de codificación AVX .

- Bulldozer GEN4 ( excavadora ) admite conjuntos de instrucciones AVX2 .

Tecnología de proceso y frecuencia de reloj

- Capa de proceso 11 de metal 32 nm SOI con implementados de primera generación GlobalFoundries 's de alta K Metal Gate (HKMG)

- Aumento del rendimiento de Turbo Core 2 para aumentar la frecuencia de reloj hasta 500 MHz con todos los subprocesos activos (para la mayoría de las cargas de trabajo) y hasta 1 GHz con la mitad del subproceso activo, dentro del límite de TDP.

- El chip funciona a 0,775 a 1,425 V, logrando frecuencias de reloj de 3,6 GHz o más.

- TDP mínimo-máximo: 25 - 140 vatios

Interfaz de caché y memoria

- Hasta 8 MB de L3 compartidos entre todos los núcleos en la misma matriz de silicio (8 MB para 4 núcleos en el segmento de escritorio y 16 MB para 8 núcleos en el segmento de servidor), divididos en cuatro subcachés de 2 MB cada uno, capaces de operar a 2.2 GHz a 1,1125 V

- Soporte de memoria nativa DDR3 hasta DDR3-1866

- Controlador de memoria integrado Dual Channel DDR3 para escritorio y servidor / estación de trabajo Opteron 42xx "Valencia"; Controlador de memoria integrado Quad Channel DDR3 para servidor / estación de trabajo Opteron 62xx "Interlagos"

- AMD afirma ser compatible con dos DIMM de DDR3-1600 por canal. Dos DIMM de DDR3-1866 en un solo canal se reducirán a 1600.

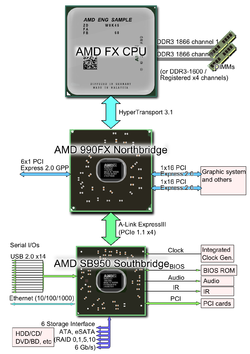

Interfaz de E / S y socket

- Tecnología HyperTransport rev. 3.1 ( 3,20 GHz, 6,4 GT / s, 25,6 GB / sy enlace ancho de 16 bits ) [implementado por primera vez en la revisión HY-D1 "Magny-Cours" en la plataforma de socket G34 Opteron en marzo de 2010 y "Lisbon" en el socket Plataforma C32 Opteron en junio de 2010]

-

Zócalo AM3 + ( AM3r2 )

- 942 pines, solo compatible con DDR3

- Conservará la compatibilidad con versiones anteriores de las placas base Socket AM3 (según la elección del fabricante de la placa base y si se proporcionan actualizaciones de BIOS), sin embargo, esto no es oficialmente compatible con AMD; Las placas base AM3 + serán compatibles con los procesadores AM3.

- Para el segmento de servidor, se utilizarán el zócalo G34 (LGA1974) y el zócalo C32 (LGA1207) existentes.

Características

Tabla de características de la CPU

Procesadores

Los primeros envíos de ingresos de procesadores Opteron basados en Bulldozer se anunciaron el 7 de septiembre de 2011. Los modelos FX-4100, FX-6100, FX-8120 y FX-8150 se lanzaron en octubre de 2011; con el resto de procesadores AMD de la serie FX lanzados a finales del primer trimestre de 2012.

Escritorio

| Modelo | [Módulos / FPU ] | Frec.

(GHz) |

Max. turbo

(GHz) |

L2

cache |

L3

(MEGABYTE) |

TDP

(W) |

DDR3

Memoria |

Turbo

Centro 2.0 |

Enchufe | |

|---|---|---|---|---|---|---|---|---|---|---|

| Lleno

carga |

Mitad

carga |

|||||||||

| FX-8100 | [4] 8 | 2.8 | 3.1 | 3,7 | 4 ×

2 MB |

8 | 95 | 1866 | sí | AM3 + |

| FX-8120 | 3.1 | 3.4 | 4.0 | 125 | ||||||

| FX-8140 | 3.2 | 3.6 | 4.1 | 95 | ||||||

| FX-8150 | 3.6 | 3.9 | 4.2 | 125 | ||||||

| FX-8170 | 3.9 | 4.2 | 4.5 | |||||||

| FX-6100 | [3] 6 | 3.3 | 3.6 | 3.9 | 3 ×

2 MB |

95 | ||||

| FX-6120 | 3.6 | 3.9 | 4.2 | |||||||

| FX-6130 | 3.6 | 3.8 | 3.9 | |||||||

| FX-6200 | 3.8 | 4.0 | 4.1 | 125 | ||||||

| FX-4100 | [2] 4 | 3.6 | 3,7 | 3.8 | 2x

2 MB |

95 | ||||

| FX-4120 | 3.9 | 4.0 | 4.1 | |||||||

| FX-4130 | 3.8 | 3.9 | 4.0 | 4 | 125 | |||||

| FX-4150 | 3.8 | 8 | 95/125 | |||||||

| FX-4170 | 4.2 | 4.3 | 125 | |||||||

Fuentes principales: CPU-World y Xbit-Labs

Servidor

Hay dos series de procesadores basados en Bulldozer para servidores : la serie Opteron 4200 ( Socket C32 , nombre en código Valencia, con hasta cuatro módulos) y la serie Opteron 6200 ( Socket G34 , nombre en código Interlagos, con hasta 8 módulos).

Demanda por publicidad falsa

En noviembre de 2015, AMD fue demandada en virtud de la Ley de recursos legales para consumidores de California y la Ley de competencia desleal por supuestamente tergiversar las especificaciones de los chips Bulldozer. La demanda colectiva, presentada el 26 de octubre en el Tribunal de Distrito de EE. UU. Para el Distrito Norte de California, afirma que cada módulo Bulldozer es, de hecho, un solo núcleo de CPU con algunas características de doble núcleo, en lugar de un verdadero diseño de doble núcleo. . En agosto de 2019, AMD acordó resolver la demanda por 12,1 millones de dólares.

Rendimiento

Rendimiento en Linux

El 24 de octubre de 2011, las pruebas de primera generación realizadas por Phoronix confirmaron que el rendimiento de la CPU Bulldozer fue algo menor de lo esperado. En muchas pruebas, la CPU se ha desempeñado al mismo nivel que la generación anterior del Phenom 1060T.

Posteriormente, el rendimiento aumentó sustancialmente, ya que se lanzaron varias optimizaciones del compilador y correcciones del controlador de la CPU.

Rendimiento en Windows

Las primeras CPU Bulldozer tuvieron una respuesta mixta. Se descubrió que el FX-8150 tuvo un desempeño deficiente en los puntos de referencia que no tenían muchos subprocesos, quedando atrás de los procesadores de la serie Intel Core i * de segunda generación y siendo igualado o incluso superado por el propio Phenom II X6 de AMD a velocidades de reloj más bajas. En los puntos de referencia con muchos subprocesos, el FX-8150 se desempeñó a la par con el Phenom II X6 y el Intel Core i7 2600K , según el punto de referencia. Dado el rendimiento general más consistente del Intel Core i5 2500K a un precio más bajo, estos resultados dejaron a muchos revisores decepcionados. Se descubrió que el procesador consumía mucha energía bajo carga, especialmente cuando estaba overclockeado, en comparación con el Sandy Bridge de Intel .

El 13 de octubre de 2011, AMD declaró en su blog que "hay algunos en nuestra comunidad que sienten que el rendimiento del producto no cumplió con sus expectativas", pero mostró puntos de referencia en aplicaciones reales en las que superó a Sandy Bridge i7 2600k y AMD X6 1100T.

En enero de 2012, Microsoft lanzó dos revisiones para Windows 7 y Server 2008 R2 que mejoran marginalmente el rendimiento de las CPU Bulldozer al abordar las preocupaciones de programación de subprocesos que surgieron después del lanzamiento de Bulldozer.

El 6 de marzo de 2012, AMD publicó un artículo de la base de conocimientos en el que se indicaba que existía un problema de compatibilidad con los procesadores FX y ciertos juegos en la plataforma de distribución de juegos digitales ampliamente utilizada, Steam . AMD declaró que habían proporcionado una actualización de BIOS a varios fabricantes de placas base (a saber: Asus , Gigabyte Technology , MSI y ASRock ) que solucionaría el problema.

En septiembre de 2014, el director ejecutivo de AMD, Rory Read, admitió que el diseño de la Bulldozer no había sido una "parte que cambia el juego" y que AMD tuvo que vivir con el diseño durante cuatro años.

Overclocking

El 31 de agosto de 2011, AMD y un grupo de overclockers conocidos, incluidos Brian McLachlan, Sami Mäkinen, Aaron Schradin y Simon Solotko, lograron establecer un nuevo récord mundial de frecuencia de CPU utilizando el procesador Bulldozer FX-8150 inédito y overclockeado. Antes de ese día, el récord estaba en 8.309 GHz, pero el Bulldozer combinado con enfriamiento de helio líquido alcanzó un nuevo máximo de 8.429 GHz. Desde entonces, Andre Yang superó el récord a 8.58 GHz usando nitrógeno líquido . El 22 de agosto de 2014 y usando un FX-8370 (Piledriver), The Stilt del Team Finland logró una frecuencia máxima de CPU de 8.722 GHz.

Revisiones

Piledriver es el nombre en clave de AMD para su microarquitectura mejorada de segunda generación basada en Bulldozer . LosnúcleosAMD Piledriver se encuentran en lasseries de APU y CPU basadasen Socket FM2 Trinity y Richland y en laserieFX de CPU basadas enSocket AM3 + Vishera . Piledriver fue la última generación de la familia Bulldozer disponible para el zócalo AM3 + y con una caché L3. Los procesadores Piledriver disponibles para zócalos FM2 (y su variante móvil) no venían con una caché L3, ya que la caché L2 es la caché de último nivel para todos los procesadores FM2 / FM2 +.

Steamroller es el nombre en clave de AMD para su microarquitectura de tercera generación basada en una versión mejorada de Piledriver . Los núcleos Steamroller se encuentran en laserie de APU y CPU basadasen Socket FM2 + Kaveri .

Excavator es el nombre en clave delnúcleo Bulldozer de cuarta generación. La excavadora se implementó como APU de la serie A 'Carrizo', APU de la serie A "Bristol Ridge" y CPU Athlon x4.

Ver también

- Lista de microarquitecturas de CPU AMD

- Lista de microprocesadores AMD FX

- Charles R. Moore (ingeniero informático)

- Alfa 21264

- K10 (microarquitectura)

- Bobcat (microarquitectura)

- Opteron

- Piledriver (microarquitectura)

- Steamroller (microarquitectura)

- Excavadora (microarquitectura)

- Zen (microarquitectura)