AMD Am29000 - AMD Am29000

El AMD Am29000 , comúnmente abreviado a 29k , es una familia de microprocesadores y microcontroladores RISC de 32 bits desarrollados y fabricados por Advanced Micro Devices (AMD). Basado en el seminal Berkeley RISC , el 29k agregó una serie de mejoras significativas. Fueron, durante un tiempo, los chips RISC más populares del mercado, ampliamente utilizados en impresoras láser de una variedad de fabricantes.

Varias versiones se introdujeron durante el período de 1988 a 1995, comenzando con el 29000. El modelo final, el 29050 , fue la primera versión superescalar , retirando hasta cuatro instrucciones por ciclo, y también incluyendo una unidad de punto flotante (FPU) muy mejorada . .

A finales de 1995, AMD abandonó el desarrollo del 29k porque el equipo de diseño se transfirió para dar soporte a la parte de PC del negocio. Lo que quedaba del negocio integrado de AMD se reorientó hacia la familia integrada 186 de derivados 80186 . La mayoría de los recursos de AMD se concentraron luego en sus clones x86 de escritorio de alto rendimiento, utilizando muchas de las ideas y partes individuales del último 29k para producir el AMD K5 .

Diseño

El 29000 evolucionó del mismo diseño Berkeley RISC que también llevó al Sun SPARC , Intel i960 , ARM y RISC-V .

Un elemento de diseño utilizado en algunos de los diseños derivados de RISC de Berkeley es el concepto de ventanas de registro , una técnica que se utiliza para acelerar significativamente las llamadas a procedimientos . La idea es usar un gran conjunto de registros como una pila, cargando datos locales en un conjunto de registros durante una llamada y marcándolos como "muertos" cuando el procedimiento regresa. Los valores que se devuelven de las rutinas se colocarán en la "página global", los ocho registros superiores en el SPARC (por ejemplo). El diseño RISC temprano de la Universidad de Stanford , el MIPS de Stanford , también consideró este concepto, pero decidió que los compiladores mejorados podrían hacer un uso más eficiente de los registros de propósito general que una ventana cableada.

En el diseño original de Berkeley, SPARC y i960, las ventanas tenían un tamaño fijo. Una rutina que usa solo una variable local aún usaría hasta ocho registros en el SPARC, desperdiciando este costoso recurso. Fue aquí donde el 29000 se diferenciaba de estos diseños anteriores, utilizando un tamaño de ventana variable. En este ejemplo, solo se usarían dos registros, uno para la variable local y otro para la dirección de retorno . También agregó más registros, incluidos los mismos 128 registros para la pila de procedimientos, pero agregando otros 64 para el acceso global. En comparación, el SPARC tenía 128 registros en total y el conjunto global era una ventana estándar de ocho. Este cambio resultó en un uso de registro mucho mejor en el 29000 bajo una amplia variedad de cargas de trabajo.

El 29000 también amplió la pila de ventanas de registro con una pila en memoria (y en teoría, en caché). Cuando la ventana se llenaba, las llamadas se empujaban desde el final de la pila de registros a la memoria, y se restauraban según fuera necesario cuando volvía la rutina. En general, el uso del registro del 29000 era considerablemente más avanzado que los diseños de la competencia basados en los conceptos de Berkeley.

Otra diferencia con el diseño de Berkeley es que el 29000 no incluía ningún registro de código de condición de propósito especial. Cualquier registro podría usarse para este propósito, permitiendo que las condiciones se guarden fácilmente a expensas de complicar algún código. Se utilizó un búfer de captación previa de instrucciones ("Caché de destino de rama") que almacenaba hasta 4 instrucciones y se utilizaba para mejorar el rendimiento durante las ramas; el 29000 no incluía ningún sistema de predicción de rama, por lo que había un retraso si se tomaba una rama (ni tampoco originalmente era superescalar , por lo que no podía "hacer ambos lados" como es común en algunos diseños). El búfer mitigó esto almacenando cuatro instrucciones del otro lado de la rama, que se podían ejecutar instantáneamente mientras el búfer se volvía a llenar con nuevas instrucciones de la memoria.

Versiones

El primer 29000 se lanzó en 1988, incluida una MMU incorporada, pero el soporte de punto flotante se descargó al 29027 FPU . Las unidades con MMU o Branch Target Cache fallidas se vendieron como 29005 .

La línea se actualizó con 29030 y 29035 , que incluían un caché de instrucciones de 8 KB o 4 KB, respectivamente. Otra actualización integró la FPU en la matriz y agregó una caché de datos de 4 KB para producir el 29040 .

La última versión de uso general fue la 29050 . Esta fue una mejora significativa del diseño original, la primera versión superescalar que podía ejecutar instrucciones fuera de orden y especulativamente . Se pueden trabajar hasta seis instrucciones al mismo tiempo a través de varias etapas de la tubería, y cuatro se pueden retirar en cualquier ciclo. El 29050 también incluyó una FPU significativamente mejorada. El 29050 estaba disponible inicialmente con frecuencias de reloj de 25, 50 y 75 MHz . Posteriormente se introdujo una versión de 100 MHz.

Varias partes del diseño 29050 se utilizaron como base para la serie K5 de procesadores compatibles con x86 . El sumador y el multiplicador FPU se transfirieron con algunos cambios de diseño, se agregó un motor de nanocódigo a la FPU para acomodar las instrucciones complejas que se encuentran en x86 pero no en el 29050, mientras que el resto del diseño del núcleo se usó junto con un microcódigo complejo para traducir instrucciones x86 a 'µops' similares a 29k sobre la marcha.

Honeywell 29KII es una cpu basada en AMD 29050 y se utilizó ampliamente en aviónica en tiempo real.

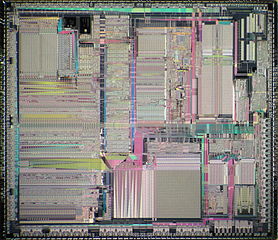

- Muere fotos

Ver también

Referencias

enlaces externos

- Guía de identificación de AMD 29k (procesador de instrucciones optimizado)

- Mann, Daniel (1995), Evaluating and Programming the 29K RISC Family (PDF) , Advanced Micro Devices, archivado desde el original (PDF) el 27 de septiembre de 2007 libro pdf sobre la familia 29k

- chipdb.org Imágenes de diferentes procesadores Am29000