RCA 1802 - RCA 1802

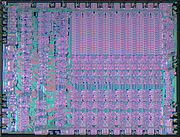

RCA CDP 1802

| |

| Información general | |

|---|---|

| Lanzado | 1974 |

| Especificaciones físicas | |

| Paquete (s) | |

El COSMAC es una familia de microprocesadores de 8 bits introducida por RCA . Es históricamente notable como el primer microprocesador CMOS . El primer modelo de producción fue el de dos chip CDP1801R y CDP1801U , que más tarde se combinaron en el chip único CDP1802 . El 1802 representó la mayor parte de la producción de COSMAC, y hoy toda la línea se conoce simplemente como RCA 1802 .

El diseño del procesador tiene su historia en una computadora doméstica experimental diseñada por Joseph Weisbecker a principios de la década de 1970, construida en su casa con componentes TTL . RCA comenzó el desarrollo de la versión CMOS del diseño del procesador en 1973, probándolo en 1974 con planes para pasar a una implementación de un solo chip de inmediato. Jerry Herzog dirigió el diseño de la versión de un solo chip, que se probó en 1975 y entró en producción en 1976.

A diferencia de la mayoría de los diseños de la época, que se fabricaron utilizando el proceso NMOS , el COSMAC se implementó en forma CMOS y utilizó lógica estática . Esto le permitió funcionar con configuraciones de energía más bajas e incluso detenerse por completo. RCA se refirió a su proceso CMOS como "semiconductor / de metal-óxido de silicio complementario", dando lugar a la acrónimo COS / MAC, que después se backronymed a "de simetría complementaria monolítico-array ordenador" cuando se refiere al procesador. RCA también produjo versiones endurecidas por radiación utilizando un proceso de silicio sobre zafiro , que encontró uso en el campo aeroespacial. Estos permanecen en uso hasta el día de hoy y continúan siendo producidos por Renesas (anteriormente Intersil ).

Los sucesores del 1802 son el CDP1804, CDP1805 y CDP1806, que tienen un conjunto de instrucciones extendido, otras características mejoradas (como RAM y ROM en el chip y temporizador incorporado), con algunas versiones que se ejecutan a velocidades de reloj más rápidas, aunque no una diferencia de velocidad significativa. Algunas características también se pierden, como la funcionalidad del cargador de arranque automático DMA. También hay algunos cambios menores en la función de los pines, pero la línea continúa produciéndose en su formato original de paquete en línea dual (DIP) de 40 pines .

Historia

FRED

Joseph Weisbecker había estado fascinado durante mucho tiempo con el potencial de las computadoras en el hogar, habiendo declarado ya en 1955 que esperaba que algún día se integraran en prácticamente todos los dispositivos. La tecnología de la época hizo imposibles las pequeñas computadoras integradas, pero la introducción del circuito integrado (IC) en la década de 1960 cambió las cosas drásticamente. En 1974 describió las posibilidades en un artículo de IEEE Computer:

Durante 20 años, el hardware de las computadoras se ha vuelto cada vez más complejo, los lenguajes más tortuosos y los sistemas operativos menos eficientes. Ahora, las microcomputadoras nos brindan a algunos de nosotros la oportunidad de volver a sistemas más simples. Las microcomputadoras económicas… podrían abrir vastos mercados nuevos.

A partir de 1970, Weisbecker comenzó el diseño de una pequeña máquina utilizando circuitos integrados de lógica de transistor-transistor (TTL) RCA para construir el procesador. Otras piezas, interruptores, lámparas y demás, tuvo que comprarlas en Radio Shack , repartiendo deliberadamente sus compras en cuatro tiendas para que nadie le preguntara por qué compraba tantas piezas. El diseño se ejecutó en octubre de 1971 y contenía 100 chips repartidos en varias placas de circuito .

El resultado, al que llamó FRED, aparentemente para Dispositivo educativo recreativo flexible, se empaquetó en una caja que no era muy diferente al Altair 8800 de unos años después, con interruptores de palanca en el panel frontal para entrada, lámparas para salida y luego agregando un teclado de almohadilla hexagonal . Weisbecker agregó nuevas funciones continuamente y en 1972 había ganado un generador de caracteres y la capacidad de cargar y guardar programas en cintas de casete .

La hija de Weisbecker, Joyce Weisbecker , se sintió atraída inmediatamente por el sistema y comenzó a escribir programas para él. Esto incluyó varios juegos, que fueron portados a máquinas posteriores basadas en COSMAC. Cuando RCA entró en el negocio de las consolas de juegos a finales de la década de 1970, estos juegos se grabaron en forma de cartucho ROM y Joyce se convirtió en la primera desarrolladora de videojuegos comercial conocida.

Liberación

Weisbecker mostró la máquina a la gerencia de RCA durante este período, pero al principio hubo poco interés. Esto fue poco después de que David Sarnoff se jubilara y entregara el puesto de director ejecutivo a su hijo, Robert Sarnoff . Robert estaba más interesado en construir el lado mediático de la compañía mientras salía con estrellas de la grabación, ignorando a RCA Laboratories a pesar de una serie de desarrollos líderes en la industria que tenían lugar allí. Parte del escepticismo mostrado por la gerencia puede haber tenido que ver con la reciente venta de la empresa de su negocio de computadoras mainframe a Sperry Rand con una gran amortización .

Con el tiempo, la empresa se interesó en el sistema y empezó a adaptarlo a su sistema de fabricación COS / MOS recién introducido. Un informe de laboratorio de 1973 se refiere a un "prototipo" que se entregó en 1972, pero es probable que se refiera a la implementación TTL original. Continúa señalando que un esfuerzo por reducir el procesador a una implementación de dos chips con entregas en COS / MOS en 1974. Es aquí donde el procesador se conoce por primera vez como COSMAC, por Computadora de matriz monolítica de simetría complementaria. Continúa afirmando que otro laboratorio producirá el sistema en un formato de silicio sobre zafiro de 8 chips , aunque la fecha es simplemente "poco después" de las versiones CMOS, y que ya se estaban planificando los planes para una versión de un solo chip. planificado.

Dispositivos COSMAC

Aunque RCA comenzó el desarrollo de COSMAC a principios de la década de 1970, pasó algún tiempo antes de que presentaran sus propios productos basados en él. En 1975, se experimentó con un prototipo de una máquina de juegos de arcade con ROM intercambiables para el negocio de las operaciones con monedas, pero finalmente se abandonó.

Mientras tanto, Weisbecker había adaptado el FRED original, conocido en RCA como System 00 en ese momento, utilizando el nuevo conjunto de chips para producir un sistema de placa única muy simplificado conocido como COSMAC ELF . Las instrucciones de construcción se describieron en un artículo de la revista Popular Electronics en 1976, y una versión ampliada con varias actualizaciones en un segundo artículo en 1977. Una característica única del ELF es que no requirió ninguna memoria de solo lectura (ROM) para el inicio. en su lugar, se utilizó el sistema de acceso directo a memoria (DMA) del procesador para leer los interruptores del panel frontal directamente en la memoria.

RCA debatió si introducir versiones preempaquetadas del ELF en el mercado. Mientras debatían, un mayor desarrollo condujo a una máquina simplificada que combinaba el ELF con un nuevo chip controlador de pantalla , el CDP1861 , para producir una consola de juegos . Durante este tiempo, Joyce fue contratada por RCA para escribir varios videojuegos para la plataforma, incluido un producto educativo estilo cuestionario en asociación con Random House , una de las muchas empresas que habían sido elegidas por las juergas de compras de RCA.

Después de un año de discusiones, la compañía finalmente decidió lanzar dos productos basados en la plataforma, una computadora en kit conocida como COSMAC VIP y una consola de juegos conocida como RCA Studio II . Las máquinas habían estado disponibles desde 1975, pero la Studio II se anunció sólo en enero de 1977, un par de meses después de que Fairchild Channel F se convirtiera en la primera máquina basada en cartuchos en el mercado. Ambos pronto serían eclipsados y olvidados en gran medida debido al lanzamiento del Atari 2600 más tarde ese año. RCA canceló el Studio II en febrero de 1978.

Uso integrado

El COSMAC fue único entre los primeros procesadores de 8 bits porque había sido diseñado explícitamente para su uso en microcomputadoras; otros diseños de la época estaban dirigidos invariablemente al espacio del procesador integrado , y los que habían sido diseñados para uso informático eran, en general, sistemas más complejos y, a menudo, de 16 bits. Aunque el COSMAC había sido diseñado para uso informático, la lenta entrada en el mercado de RCA y los intentos infructuosos en este mercado finalmente fracasaron y otros procesadores como el MOS 6502 y Zilog Z80 llegarían a dominar este mercado. Irónicamente, COSMAC finalmente encontraría un gran éxito en el mercado integrado, porque su diseño CMOS le permitía trabajar con menor potencia. A fines de la década de 1970, se usaba ampliamente en muchos entornos industriales, y especialmente en el aeroespacial. El 1802 dirigió la sonda Galileo a Júpiter en 1989, y sigue utilizándose en funciones similares hasta el día de hoy.

Aplicaciones

Sistemas de microcomputadoras

Varios de los primeros microordenadores se basaron en el 1802, incluidos COSMAC ELF (1976), Netronics ELF II , Quest SuperELF , COSMAC VIP , Comx-35 , Finnish Telmac 1800 , Telmac TMC-600 y Oscom Nano , Yugoslav Pecom 32 y 64 y los sistemas Cybervision vendidos a través de Montgomery Ward a fines de la década de 1970, así como la consola de videojuegos RCA Studio II (una de las primeras consolas en usar gráficos de mapa de bits ). El sistema de entrenamiento por computadora de placa única Edukit , similar a un COSMAC Elf ampliado , fue ofrecido por Modus Systems Ltd. en Gran Bretaña a principios de la década de 1980. Infinite Incorporated produjo un entrenador de computadora de consola expandible de bus S-100 basado en 1802 a fines de la década de 1970 llamado UC1800, disponible ensamblado o en forma de kit.

Como parte del trabajo de los aficionados a la retrocomputación de 1802 , se han construido otras computadoras más recientemente (posteriores a 2000), incluido el kit de microcomputadora Membership Card que cabe en una lata de Altoids y el Spare Time Gizmos Elf 2000 (Elf 2K), entre otros. Ver § Emuladores y simuladores para otros sistemas.

Integración de productos

El 1802 también se utilizó en instrumentos científicos y productos comerciales.

Los vehículos Chrysler posteriores a 1980 y los modelos asociados utilizan el 1802 en su sistema electrónico de combustión reducida de segunda generación, con control de chispa electrónico, uno de los primeros sistemas de control automáticos a bordo basados en computadora.

El 1802 se utilizó en la fabricación de muchas máquinas de pinball y videojuegos en España.

Endurecimiento por radiación

Además de la tecnología C2L CMOS de "silicio a granel", el 1802 también estaba disponible fabricado en tecnología de proceso de semiconductores de silicio sobre zafiro (SOS), que le confiere un grado de resistencia a la radiación y descarga electrostática (ESD). Junto con sus capacidades de extrema baja potencia, esto hace que el chip sea adecuado para aplicaciones espaciales y militares (además, en el momento en que se introdujo el 1802, muy pocos, si es que había alguno, otros microprocesadores endurecidos por radiación estaban disponibles en el mercado). La versión 1802 endurecida por radiación fue fabricada en Sandia National Laboratories de acuerdo con RCA.

Ciencia y tecnología espacial

El 1802 se utilizó en muchos programas, experimentos, proyectos y módulos de naves espaciales y ciencias espaciales, como la nave espacial Galileo , Magellan , varios satélites en órbita terrestre y satélites que transportan radioaficionados.

También se ha verificado a partir de la documentación fuente de la NASA que el 1802 se ha utilizado en el Telescopio Espacial Hubble .

Lenguajes de programación

El primer lenguaje de alto nivel disponible para 1802 fue Forth , proporcionado por Forth, Inc. y fue conocido como MicroFORTH, en 1976 (ver el archivo de Forth Inc). Otros lenguajes de programación disponibles, tanto intérpretes como compiladores, son CHIP-8 (y variantes), 8th (una versión de Forth creada por Lee Hart), Tiny BASIC de Tom Pittman , C, varios ensambladores y ensambladores cruzados, y otros. Agencias federales como la NASA y sus instalaciones utilizaron otros lenguajes especializados, incluidos Johnson Space Center, AMES, Goddard, Langley, Marshall y Jet Propulsion Laboratory (JPL), que incluían el compilador cruzado HAL / S, STOIC , un Forth -como el lenguaje, y otros.

Interpreter for Process Structures (IPS), un lenguaje de programación y entorno de desarrollo, fue escrito y utilizado específicamente para el control en tiempo real de los satélites AMSAT .

Emuladores y simuladores

El chip 1802 y las computadoras que utilizan el microprocesador han sido emulados y simulados en hardware y / o software por aficionados. Hay tres diseños en VHDL para una FPGA . Se creó un clon COSMAC Elf de velocidad completa y precisión de bus sin un chip de microprocesador CDP1802 o un chip de video CDP1861 utilizando microcontroladores PIC . Un simulador en línea del COSMAC Elf (mejorado) escrito en JavaScript se ejecuta en el navegador del usuario sin necesidad de descargarlo.

Descripción

Introducción

El RCA 1802 tiene un diseño CMOS de núcleo estático sin frecuencia de reloj mínima , por lo que puede funcionar a velocidades muy bajas y baja potencia, incluida una frecuencia de reloj de cero para suspender el microprocesador sin afectar su funcionamiento.

Tiene dos buses separados de 8 pines: un bus de datos bidireccional de 8 bits y un bus de direcciones multiplexadas en el tiempo , con acceso a los 8 bits de orden alto y bajo de la dirección de 16 bits en ciclos de reloj alternativos. Esto contrasta con la mayoría de los diseños de la época, como el MOS 6502 y el Intel 8080 , que usaban un bus de direcciones de 16 bits.

El 1802 tiene un puerto de salida (Q) programable y comprobable de un solo bit , y cuatro pines de entrada que se prueban directamente mediante instrucciones de derivación (EF1-EF4). Estos pines permiten que las tareas simples de entrada / salida (E / S) se manejen directamente y se programen fácilmente.

Debido a que las instrucciones tardaron entre 8 y 16 ciclos de reloj en completarse, el 1802 no fue particularmente rápido. A modo de comparación, el 6502 completa la mayoría de las instrucciones en 2 a 4 ciclos de reloj, y el más largo toma 7 ciclos.

Designaciones de sufijo de número de pieza

Varios sufijos del número de pieza CDP1802 indican especificaciones técnicas, que incluyen (A, B y C) velocidad de funcionamiento (3,2 MHz a 6,4 MHz), temperatura (-40 ° C a +85 ° C, -55 ° C a +125 ° C) y rangos de voltaje (4 V a 10,5 V), tipo de paquete (D, E, Q) y quemado (X). Estos estaban algo estandarizados entre los diversos proveedores de origen, incluidos RCA, Intersil, Harris, Hughes Aircraft y Solid State Scientific (SSS). Hughes usó el prefijo HCMP y SSS usó el prefijo SCP (y posiblemente BCP), en lugar de CDP, y tenía sufijos adicionales que aún no se han documentado. (ejemplos: CDP1802A, CDP1802ACE, CDP1802BCD, HCMP1802AP, SCP1802D)

| Sufijo | Tipo de paquete |

|---|---|

| mi | PDIP = Paquete de plástico doble en línea |

| D | SBDIP = Paquete en línea doble de cerámica soldada lateralmente |

| Q | PLCC = Portador de virutas de plástico con plomo |

| X | Quemado |

Registros y E / S

El 1802 es una máquina de bytes de 8 bits, con soporte mínimo para operaciones de 16 bits, excepto mediante la manipulación de 2 bytes. El acumulador primario es el registro 'D' de 8 bits (registro de datos). La bandera de acarreo de un solo bit es DF (bandera de datos). La mayoría de las operaciones utilizan el registro D, incluidas las funciones aritméticas y lógicas, y las instrucciones de almacenamiento y carga de referencia a la memoria. La mayoría de las operaciones de 16 bits tienen que trabajar en el byte inferior y luego en el byte superior, a través de D, utilizando el DF como acarreo y préstamo según sea necesario.

Una característica importante del 1802 es un conjunto de dieciséis registros de 16 bits cada uno, que se utilizan principalmente para direccionamiento. Con la instrucción SEP, puede seleccionar cualquiera de los 16 registros para que sea el contador del programa ; utilizando la instrucción SEX , puede seleccionar cualquiera de los registros de 16 bits para que sea el registro de índice . El registro R0 tiene el uso especial de mantener la dirección de memoria para el controlador DMA incorporado . El registro R1 tiene el uso especial de ser el contador de programa para el manejador de interrupciones.

Hay instrucciones que permiten configurar y leer los valores en estos registros a través de D, trabajando por separado los 8 bits superior e inferior a la vez. También hay instrucciones para realizar incrementos y decrementos de todo el valor de 16 bits, y algunas instrucciones realizan incrementos y decrementos automáticos, como LDA (avance de carga) y STXD (almacenamiento mediante X y decremento). Las comparaciones de valores y registros de 16 bits también necesitarían usar el registro D como intermediario, usando múltiples instrucciones para realizar las operaciones.

El procesador tiene cinco líneas de E / S especiales . Hay una única salida Q que se puede configurar con la instrucción SEQ y restablecer con la instrucción REQ. Hay cuatro entradas de bandera externas de un solo bit, EF1, EF2, EF3 y EF4, y hay ocho instrucciones de bifurcación dedicadas para bifurcar condicionalmente según el estado de esas líneas de entrada. Hay siete instrucciones de puerto de entrada y siete de salida que utilizan el registro RX y el acumulador D.

Las líneas EF y Q se usaban típicamente para múltiples interfaces en computadoras de aficionados basadas en 1802 debido al fácil y favorable manejo de las líneas. Era típico que la línea Q activara un LED de estado , una interfaz de casete , una interfaz RS-232 y el altavoz. Esto significaba que el usuario podía escuchar la transmisión de datos de casete y RS-232 (a menos que se implementara un control de volumen). Tradicionalmente, la línea EF4 se conecta al botón pulsador momentáneo INPUT del COSMAC Elf. Otros sistemas pueden usar una de las otras líneas.

Hay otros registros y banderas de uso especial, algunos internos y otros utilizables mediante programación: N, P, X e I de 4 bits; T de 8 bits; e IE de 1 bit.

Derivación

Hay tres tipos de ramificación incondicional y condicional en 1802, corta y larga, y saltos.

Las ramas cortas son instrucciones de 2 bytes y utilizan un rango de 256 bytes, dirección de un solo byte, direccionamiento absoluto de página en el rango de 0 a 255 (FF hexadecimal). No hay ramificación relativa. La rama corta siempre salta dentro de la página que contiene el byte de dirección.

Las ramas largas utilizan direcciones completas de 16 bits para admitir el espacio de direcciones de memoria de 64 K, y son las únicas instrucciones de 3 bytes.

Las instrucciones de salto incrementan la PC en uno para los saltos cortos incondicionales, o dos para los saltos largos. Solo el Long Skip tiene ramificación condicional.

Llamadas a subrutinas

El procesador no tiene una dirección CALL de subrutina estándar ni instrucciones RET, aunque se pueden simular. El diseño de 16 registros hace posible algunos mecanismos interesantes de llamada y retorno de subrutinas, aunque se adaptan mejor a programas pequeños que a la codificación de propósito general.

Algunas subrutinas de uso común se pueden llamar rápidamente manteniendo su dirección en uno de los 16 registros; sin embargo, la subrutina llamada debe saber (codificado) cuál es el registro de la PC que llama para realizar la instrucción de "retorno". La instrucción SEP se usa para llamar a una subrutina apuntada por uno de los registros de 16 bits y otro SEP para regresar a la persona que llama (SEP significa Set Program Counter , y selecciona cuál de los 16 registros se usará como el programa contador desde ese punto en adelante). Antes de que una subrutina regrese, salta a la ubicación inmediatamente anterior a su punto de entrada, de modo que después de que la instrucción SEP "return" devuelva el control al llamador, el registro apuntará al valor correcto para el siguiente uso. (el procesador siempre incrementa la PC después de la referencia y el uso (recuperando la siguiente instrucción para ejecutar), por lo que esta técnica funciona como se indica)

Una variación interesante de este esquema es tener dos o más subrutinas en un anillo para que se llamen en orden de operación por turnos. En las primeras computadoras de aficionados, trucos y técnicas como esta se usaban comúnmente en la interrupción de actualización horizontal para reprogramar la dirección de la línea de escaneo para repetir cada línea de escaneo cuatro veces para el controlador de video.

Una rutina muy conocida y de uso frecuente se conoce como SCRT (Técnica estándar de LLAMADA y DEVOLUCIÓN), que permite la llamada y devolución de subrutinas de propósito general, incluido el paso de parámetros "en línea" y subrutinas anidadas usando una pila. Aunque cualquiera de los registros disponibles se puede usar para esta técnica, según la preferencia del programador, muchos usan la rutina proporcionada por RCA en el Manual del usuario CDP1802, donde el uso de registro sugerido es R2 = Stack Pointer, R3 = General Program Counter (PC), R4 = Llamar, R5 = Regresar, R6 = Puntero de argumentos pasados (no destructivo). Aunque estas rutinas de apoyo son pequeñas, existe una sobrecarga de velocidad de ejecución al usarlas. (a diferencia de lo que se incurriría si las instrucciones CALL y RET reales fueran parte del diseño del microprocesador) Esta configuración permite que R0 se use para DMA y R1 para interrupciones, si se desea, permitiendo R7 a RF (hexadecimal) para general. uso del programa.

Modos de direccionamiento

Debido al bus de direcciones de 16 bits y al bus de datos de 8 bits, los dieciséis registros de propósito general tienen 16 bits de ancho, pero el registro D del acumulador tiene solo 8 bits de ancho. El acumulador, por tanto, tiende a ser un cuello de botella. Transferir el contenido de un registro a otro implica cuatro instrucciones (una Get y una Put en el byte HI del registro, y un par similar para el byte LO: GHI R1; PHI R2; GLO R1; PLO R2). De manera similar, cargar una nueva constante en un registro (como una nueva dirección para un salto de subrutina, o la dirección de una variable de datos) también involucra cuatro instrucciones (dos instrucciones de carga inmediata, LDI, una para cada mitad de la constante, cada una seguida de una instrucción Put en el registro, PHI y PLO).

Los dos modos de direccionamiento Registro indirecto y Registro indirecto con incremento automático son entonces bastante eficientes para realizar operaciones de 8 bits en los datos en el acumulador. Sin embargo, no hay otros modos de direccionamiento. Por lo tanto, el modo de direccionamiento directo debe emularse utilizando las cuatro instrucciones mencionadas anteriormente para cargar la dirección en un registro de reserva; seguido de una instrucción para seleccionar ese registro como registro de índice; seguido, finalmente, por la operación prevista en la variable de datos a la que apunta esa dirección.

DMA y modo de carga

El CDP1802 tiene un controlador DMA integrado simple , con dos líneas de solicitud DMA para entrada y salida DMA. La CPU solo accede a la memoria durante ciertos ciclos del ciclo de máquina de varios pasos, que requirió entre 8 y 16 ciclos de reloj. El hardware externo podría leer o escribir datos durante estos períodos sin interrumpir el procesador, un concepto general conocido como robo de ciclo .

R0 se utiliza como puntero de dirección DMA. La dirección de inicio de los datos DMA se colocaría en R0 y luego se tiraría del pin de lectura o escritura apropiado en la CPU baja. La CPU respondió a la solicitud de DMA incrementando el valor en R0, de modo que la siguiente solicitud se almacena automáticamente en la siguiente ubicación en la memoria. Por lo tanto, simplemente activando repetidamente los pines DMA, el sistema recorrería toda la memoria.

El controlador DMA también proporciona un "modo de carga" especial, que permite cargar la memoria mientras las entradas CLEAR y WAIT del procesador están activas. Esto permite que un programa se cargue sin la necesidad de un cargador de arranque basado en ROM. Esto fue utilizado por la microcomputadora COSMAC Elf y sus sucesores para cargar un programa desde interruptores de palanca o un teclado hexadecimal sin necesidad de software y hardware mínimo. El usuario podría simplemente configurar los interruptores al siguiente valor, alternar la lectura y luego continuar. No hubo necesidad de cambiar las direcciones, eso se hizo automáticamente mediante el paso de DMA.

Tiempo de instrucción

La eficiencia del ciclo de reloj es pobre en comparación con la mayoría de los microprocesadores de 8 bits. Ocho ciclos de reloj constituyen un ciclo de máquina. La mayoría de las instrucciones necesitan dos ciclos de máquina (16 ciclos de reloj) para ejecutarse; las instrucciones restantes toman tres ciclos de máquina (24 ciclos de reloj). En comparación, la tecnología MOS 6502 tarda de dos a siete ciclos de reloj para ejecutar una instrucción, y el Intel 8080 tarda de cuatro a 18 ciclos de reloj.

Chips de soporte

Gráficos

En las primeras microcomputadoras basadas en 1802, el chip controlador de visualización de video de gráficos complementarios , RCA CDP1861 (para el formato de video NTSC , variante CDP1864 para PAL ), usaba el controlador DMA incorporado para mostrar gráficos de mapas de bits en blanco y negro en pantallas de TV estándar. El 1861 también se conocía como el sistema de gráficos Pixie.

Aunque las versiones más rápidas de 1802 podían funcionar a 4-5 MHz (a 5 V; era más rápido (6,4 MHz) a 10 V), normalmente funcionaba a 3,58 MHz, dividido por 2 (1,79 MHz) para satisfacer los requisitos de el chip 1861, que daba una velocidad de poco más de 100.000 instrucciones por segundo, aunque algunas corrían a otras velocidades como ~ 2,8 MHz del Comx o 5 MHz del Pecom . El COSMAC VIP , que integró el chip de video con el procesador como una sola computadora especialmente diseñada (en lugar de como un complemento de un kit de aficionado), ejecutó notablemente el 1802 mucho más lento, sincronizándolo exactamente con el 1861, a una velocidad no determinada. -Estándar 1.76064 MHz, como se recomienda en el diseño de referencia de la hoja de especificaciones de Pixie.

El IC del circuito generador de color CDP1862, un chip complementario de 1861, podría usarse para generar gráficos en color. Algunos sistemas informáticos, como el Pecom 64 , utilizaban el VIS (sistema de interfaz de vídeo), que consta de los circuitos integrados complementarios CDP1869 y CDP1870, para obtener gráficos en color de resolución claramente superior, comparables a otros sistemas de 8 bits de la década de 1980.

Muestras de código

Este ejemplo de fragmento de código es una rutina de diagnóstico que prueba las operaciones de ALU ( unidad aritmética y lógica).

.. TEST ALU OPS 0000 90 GHI 0 .. SET UP R6 0001 B6 PHI 6 0002 F829 LDI DOIT .. FOR INPUT OF OPCODE 0004 A6 PLO 6 0005 E0 SEX 0 .. (X=0 ALREADY) 0006 6400 OUT 4,00 .. ANNOUNCE US READY 0008 E6 SEX 6 .. NOW X=6 0009 3F09 BN4 * .. WAIT FOR IT 000B 6C INP 4 .. OK, GET IT 000C 64 OUT 4 .. AND ECHO TO DISPLAY 000D 370D B4 * .. WAIT FOR RELEASE 000F F860 LDI #60 .. NOW GET READY FOR 0011 A6 PLO 6 .. FIRST OPERAND 0012 E0 SEX 0 .. SAY SO 0013 6401 OUT 4,01 0015 3F15 BN4 * 0017 E6 SEX 6 .. TAKE IT IN AND ECHO 0018 6C INP 4 .. (TO 0060) 0019 64 OUT 4 .. (ALSO INCREMENT R6) 001A 371A B4 * 001C E0 SEX 0 .. DITTO SECOND OPERAND 001D 6402 OUT 4,02 001F E6 SEX 6 0020 3F20 LOOP: BN4 * .. WAIT FOR IT 0022 6C INP 4 .. GET IT (NOTE: X=6) 0023 64 OUT 4 .. ECHO IT 0024 3724 B4 * .. WAIT FOR RELEASE 0026 26 DEC 6 .. BACK UP R6 TO 0060 0027 26 DEC 6 0028 46 LDA 6 .. GET 1ST OPERAND TO D 0029 C4 DOIT: NOP .. DO OPERATION 002A C4 NOP .. (SPARE) 002B 26 DEC 6 .. BACK TO 0060 002C 56 STR 6 .. OUTPUT RESULT 002D 64 OUT 4 .. (X=6 STILL) 002E 7A REQ .. TURN OFF Q 002F CA0020 LBNZ LOOP .. THEN IF ZERO, 0032 7B SEQ .. TURN IT ON AGAIN 0033 3020 BR LOOP .. REPEAT IN ANY CASE

Nota: La rutina anterior supone que el microprocesador CDP1802 se encuentra en un estado de reinicio inicial (o que se ha configurado como tal antes de ejecutar este código). Por lo tanto, el contador de programa (PC) y el "puntero" del registro indirecto X se establecen ambos en el registro R0 de 16 bits. Es por eso que puede generar un valor inmediato, como en el ejemplo 'OUT 4,00', porque PC y X apuntan a R0. La PC se incrementa después de que el byte de instrucción del código de operación se recupera de la memoria, por lo que apunta a la siguiente dirección cuando se ejecuta OUT 4. Por lo tanto, genera el valor en la memoria al que apunta RX = R0, que es el siguiente byte inmediato. La instrucción OUT también incrementa el registro X, que es R0, que también es el PC, por lo que genera el valor inmediato después de OUT y continúa la ejecución del programa en la siguiente dirección de instrucción después del valor inmediato. Es por eso que ve el conjunto de rutinas X (SEX) para registrar R6 y R0 según sea necesario. También tenga en cuenta que, aunque el código de operación OUT incrementa el registro RX, para generar fácilmente una sección de memoria ('búfer'), INP no lo hace. Almacena el valor en la dirección apuntada por RX y en el acumulador de bytes de datos D de 8 bits, pero RX no se modifica.

La rutina también supone que OUT 4 mostrará el valor en el LED de 8 bits del sistema de la CPU o en la pantalla hexadecimal de 2 dígitos, y IN 4 obtiene el valor de los ocho interruptores de palanca (o posiblemente el teclado hexadecimal). El código de operación BN4 (lazo; * = 'esta dirección'), "bifurca si la línea de entrada EF4 de un solo bit es baja", se usa para probar si se presiona el botón momentáneo 'Entrada'. El bucle del código de operación B4 ('if hi') espera a que se suelte el botón. SEQ y REQ encienden y apagan la línea Q única, que generalmente está unida a un LED.

El 1802 es una "máquina de bytes", pero tiene 16 registros de 16 bits, R0-RF (a veces denominado 0-F sin el prefijo 'R'). Para tratar con datos de registro de 16 bits, el programador debe obtener y poner los valores Hi o Lo de los registros utilizando el acumulador D como intermediario. Estos bytes altos y bajos de los registros a veces se denominan Rn.0 (lo) y Rn.1 (hi). Las ramas cortas son códigos de operación de 2 bytes con direccionamiento absoluto de página y un límite de dirección de 256 bytes. Las ramas largas son códigos de operación de 3 bytes con bifurcación de direcciones completa de 16 bits.

Esta información debería hacer que la rutina sea más comprensible para cualquier programador de computadoras que tenga el conocimiento suficiente para leer "pseudocódigo" y esté mínimamente familiarizado con la programación en lenguaje ensamblador y máquina.

Notas

Referencias

Citas

Bibliografía

- Informe de investigación 1973 (PDF) (Informe técnico). Laboratorios RCA. 1973.

- Cass, Stephen (2 de julio de 2018). "Chip Hall of Fame: RCA CDP 1802" . Espectro IEEE .

- Edwards, Benj (27 de octubre de 2017). "Redescubriendo a la primera diseñadora de videojuegos perdida de la historia" . Empresa rápida . Consultado el 27 de octubre de 2017 .

- Weisbecker, Joe (marzo de 1974). "Una arquitectura de microcomputadora simplificada". Computadora IEEE . 7 (3): 41–47. doi : 10.1109 / MC.1974.6323475 .

enlaces externos

- Hoja de datos CDP1802A / AC / BC, 1997 ( PDF )

- Hoja de datos CDP1802AC / 3, 2008 ( PDF )

- Sitio web de COSMAC ELF

- Un curso corto de programación (texto de 1980 sobre ensamblador RCA 1802)

- Disparo de alta resolución

Algunas partes menores de este artículo se basaron originalmente en material del Diccionario gratuito en línea de informática , que tiene licencia de la GFDL .