NS32000 - NS32000

El NS32000 , a veces conocido como 32k , es una serie de microprocesadores producidos por National Semiconductor . El primer miembro de la familia llegó al mercado en 1982, brevemente conocido como 16032 antes de convertirse en 32016 . Fue el primer microprocesador de propósito general de 32 bits del mercado. Sin embargo, el 32016 contenía una gran cantidad de errores y, a menudo, no se podía ejecutar a su velocidad nominal. Estos problemas, y la presencia de un Motorola 68000 similar que había estado disponible durante algún tiempo, llevaron a que casi no se usara en el mercado.

Siguieron varias versiones mejoradas, incluida la 32032 de 1985, que era esencialmente una 32016 con errores corregidos con un bus de datos externo de 32 bits. Si bien ofrecía aproximadamente un 50% más de velocidad que el 32016, fue superado por el Motorola 68020 de 32 bits , lanzado un año antes. El 32532 , lanzado en 1987, superó al Motorola 68030 contemporáneo en casi dos veces, pero en ese momento la mayor parte del interés en los microprocesadores se había vuelto hacia las plataformas RISC y este excelente diseño casi no se usó tampoco.

National estaba trabajando en nuevas mejoras en el 32732 , pero finalmente dejó de intentar competir en el espacio de la unidad central de procesamiento (CPU). En cambio, la arquitectura básica 32000 se combinó con varios sistemas de soporte y se relanzó como el microcontrolador Swordfish . Esto tuvo cierto éxito en el mercado antes de ser reemplazado por la arquitectura CompactRISC a mediados de la década de 1990.

Concepto de diseño

La serie NS32000 tiene su historia en un esfuerzo de National Semiconductor para producir una implementación de un solo chip de la arquitectura VAX-11 . El VAX es bien conocido por su arquitectura de conjunto de instrucciones (ISA) altamente "ortogonal" , en la que cualquier instrucción se puede aplicar a cualquier dato. Por ejemplo, una ADDinstrucción puede agregar el contenido de dos registros de procesador , o un registro contra un valor en la memoria, dos valores en la memoria o usar el registro como un desplazamiento contra una dirección. Esta flexibilidad se consideró el modelo de diseño en la era de las computadoras con conjuntos de instrucciones complejos (CISC).

National llevó a DEC a los tribunales en California para garantizar la legalidad del diseño, pero cuando DEC trasladó la demanda a Massachusetts, el estado de origen de DEC, la demanda se retiró y en su lugar se desarrolló la arquitectura de la Serie 32000. Aunque la nueva arquitectura del conjunto de instrucciones no era compatible con VAX-11, mantuvo su filosofía de diseño altamente " ortogonal ". Es decir, cada instrucción podría usarse con cualquier tipo de datos. Los artículos de la época también se refieren a esto como "simétrico".

La familia de procesadores original consistía en la CPU NS16032 y una variante de bajo consumo NS16C032, ambas con una ruta de datos de 16 bits y, por lo tanto, requerían dos ciclos de máquina para cargar una sola palabra de 32 bits. Ambos se podían usar con la unidad de administración de memoria NS16082 , que brindaba soporte de memoria virtual de 24 bits para hasta 16 MB de memoria física. El NS16008 era una versión reducida con una ruta de datos externos de 8 bits y sin soporte de memoria virtual, que tenía un número reducido de pines y, por lo tanto, era algo más fácil de implementar.

Al mismo tiempo, National también anunció dos versiones futuras, NS32032 y NS32132. El primero era esencialmente una versión del NS16032 con un bus de datos externo de 32 bits, lo que le permitía leer datos al doble de velocidad. Este fue un proyecto para ser lanzado en 1984. El NS32132 era una versión con direcciones internas de 29 bits y externas de 32 bits, lo que le permitía direccionar una memoria completa de 4 GB. Iba a ser lanzado en 1985.

Todos estos también se pueden utilizar con la unidad de punto flotante NS16081.

Arquitectura

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Los procesadores tienen 8 registros de 32 bits de propósito general, además de una serie de registros de propósito especial:

- Puntero de marco

- Puntero de pila (uno para cada modo de usuario y supervisor)

- Registro base estático, para referenciar variables globales

- Registro base de enlace para módulos enlazados dinámicamente (orientación a objetos)

- Contador de programa

- Un registro de estado de procesador típico, con un byte de usuario de orden inferior y un byte de sistema de orden superior.

(Los registros del sistema adicionales no aparecen en la lista).

El conjunto de instrucciones pertenece en gran medida al modelo CISC , con instrucciones de 2 operandos, operaciones de memoria a memoria, modos de direccionamiento flexibles y codificación de instrucciones alineadas por bytes de longitud variable. Los modos de direccionamiento pueden involucrar hasta dos desplazamientos y dos direcciones indirectas de memoria por operando, así como indexación escalada, lo que hace que la instrucción más larga imaginable sea de 23 bytes. El número real de instrucciones es mucho menor que el de los procesadores RISC actuales.

A diferencia de otros procesadores, no se proporciona autoincremento del registro base; la única excepción es un modo de direccionamiento "superior" que muestra fuentes y envía destinos. De manera única, el tamaño del desplazamiento se codifica en sus bits más significativos: 0, 10 y 11 precedidos de desplazamientos con signo de 7, 14 y 30 bits. (Aunque los procesadores son, por lo demás, consistentemente little-endian, los desplazamientos en el flujo de instrucciones se almacenan en orden big-endian).

Los operandos de propósito general se especifican mediante un campo de 5 bits. A esto se le puede agregar un byte de índice (especificando el registro de índice y la dirección base de 5 bits) y hasta 2 desplazamientos de longitud variable por operando.

32016

El primer chip de la serie se denominó originalmente 16032, pero luego se renombró como 32016 para enfatizar sus componentes internos de 32 bits. Esto lo contrasta con su principal competidor en este espacio, el Motorola 68000 (68k) de 1979 . El 68k usaba instrucciones y registros de 32 bits, pero su unidad aritmética lógica (ALU), que controla gran parte de la tarea de procesamiento general, era de solo 16 bits. Esto significaba que tenía que realizar un ciclo de datos de 32 bits a través de la ALU dos veces para completar una operación. Por el contrario, el NS32000 tiene una ALU de 32 bits, por lo que las instrucciones de 16 y 32 bits tardan el mismo tiempo en completarse.

El 32016 se envió por primera vez en 1982 en un paquete DIP de 46 pines . Puede haber sido el primer chip de 32 bits en llegar a la producción y venta en masa (al menos según el marketing de National). Sin embargo, en un informe en una publicación de junio de 1983, se señaló que National estaba "prometiendo cantidades de producción este verano" de 16032 piezas, habiendo estado "enviando cantidades de muestra durante varios meses", con el muestreo del coprocesador de coma flotante "este mes. ". Aunque una introducción de 1982 es posterior al 68k en aproximadamente dos años, el 68k aún no se estaba utilizando ampliamente en el mercado y el 32016 generó un interés significativo. Desafortunadamente, las primeras versiones estaban llenas de errores y rara vez se podían ejecutar a su velocidad nominal. En 1984, después de dos años, la lista de erratas todavía contenía elementos que especificaban condiciones incontrolables que harían que el procesador se detuviera, lo que obligaría a restablecerlo.

La hoja de ruta del producto original preveía partes de 6 MHz y 10 MHz durante 1983 y partes de 12 MHz y 14 MHz durante 1984. Sin embargo, los informes de prensa en 1984 indicaron dificultades para mantener esta hoja de ruta, ya que, según se informa, tomó cinco meses aumentar la frecuencia de la partes de 6 MHz a 8 MHz, y los representantes estiman otros "dos, tres o cinco meses" para aumentar la frecuencia a 10 MHz. Se informó que dos chips no especificados de los cinco en el conjunto de chips eran la causa de estos problemas. Un artículo de principios de 1985 sobre la estación de trabajo Whitechapel MG-1 basada en 32016 señalaba que la unidad de gestión de memoria 32081 estaba "sufriendo errores" y se había colocado en su propia placa proporcionando correcciones de hardware.

National cambió su metodología de diseño para permitir la producción de la pieza y se desarrolló conjuntamente un sistema de diseño basado en el lenguaje "Z" con la Universidad de Tel-Aviv, cerca del centro de diseño "NSC" en Herzliya , Israel. . El lenguaje "Z" es similar al Verilog y VHDL de hoy , pero tiene una sintaxis similar a Pascal y está optimizado para diseños de reloj de dos fases . Sin embargo, para cuando el fruto de estos esfuerzos se estaba sintiendo en el diseño, numerosas máquinas 68k ya estaban en el mercado, en particular la Apple Macintosh , y la 32016 nunca tuvo un uso generalizado.

El 32016 tiene un bus de datos externo de 16 bits , un bus de direcciones externas de 24 bits y un conjunto completo de instrucciones de 32 bits . También incluye una interfaz de coprocesador , lo que permite que los coprocesadores, como FPU y MMU, se conecten como pares al procesador principal. La MMU se basa en la memoria virtual de paginación por demanda , que es la característica más inusual en comparación con el enfoque de memoria segmentada utilizado por la competencia, y se ha convertido en el estándar de cómo se diseñan los microprocesadores en la actualidad. La arquitectura admite un mecanismo de reinicio de instrucciones en una falla de página, que es mucho más limpio que el enfoque de Motorola para volcar el estado interno en una falla de página, que debe volver a leerse antes de continuar la instrucción.

Aunque a menudo se compara con el conjunto de instrucciones del 68k, esto fue rechazado por los empleados de NSC; una de las frases de marketing clave de la época era "La elegancia lo es todo", comparando la serie 32000 altamente ortogonal con la "kludge". Una diferencia clave es el uso de Motorola de registros de direcciones y registros de datos, con instrucciones que solo funcionan en registros de direcciones o de datos. La Serie 32000 tiene registros de propósito general.

32032

El 32032 se introdujo en 1984. Es casi completamente compatible con el 32016, pero cuenta con un bus de datos de 32 bits (aunque mantiene el bus de direcciones de 24 bits) para un rendimiento algo más rápido. También había un 32008, un 32016 con un bus de datos reducido a 8 bits de ancho para aplicaciones de bajo costo. Es filosóficamente similar al MC68008 e igualmente impopular.

National también produjo una serie de chips de soporte relacionados como NS32081 Floating Point Unit (FPU), NS32082 Memory Management Units (MMU) , NS32203 Direct Memory Access (DMA) y NS32202 Interrupt Controllers. Con el conjunto completo más los chips de memoria y los periféricos, era factible construir un sistema informático de 32 bits capaz de admitir sistemas operativos modernos multitarea, algo que antes solo era posible en costosas minicomputadoras y mainframes .

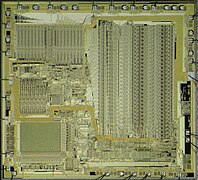

- Muere fotos

32332, 32532

En 1985, National Semi introdujo el NS32332, una versión muy mejorada del 32032. De la hoja de datos, las mejoras incluyen "la adición de un nuevo hardware de direccionamiento dedicado (que consiste en una ALU de alta velocidad, una palanca de cambios de barril y un registro de direcciones), una cola de captación previa de instrucciones aumentada (20 bytes) muy eficiente, una nueva interfaz / protocolo de bus de sistema / memoria, un protocolo de procesador esclavo de mayor eficiencia y, finalmente, mejoras del microcódigo ". También hubo una nueva NS32382 MMU, NS32381 FPU y la (muy rara) interfaz NS32310 para un Weitek FPA. El aumento de rendimiento agregado del NS32332 a partir de estas mejoras solo lo hizo un 50 por ciento más rápido que el NS32032 original y, por lo tanto, menos que el del principal competidor, el MC68020 .

National Semi introdujo el NS32532 a principios de 1987. Corriendo a 20, 25 y 30 MHz, fue un rediseño completo de la implementación interna con una canalización de cinco etapas, un Cache / MMU integrado y un rendimiento de memoria mejorado, por lo que el doble de rendimiento que los modelos MC68030 e i80386 de la competencia . En esta etapa, las arquitecturas RISC estaban comenzando a hacer incursiones, y los principales competidores se convirtieron en los ahora igualmente muertos AM29000 y MC88000 , que se consideraban más rápidos que el NS32532. Para punto flotante, el NS32532 utilizó la interfaz NS32381 o NS32580 existente para un FPA de Weitek. El NS32532 fue la base del PC532 , un proyecto de hardware de "dominio público", y uno de los pocos en producir una máquina útil que ejecuta un sistema operativo real (en este caso, Minix o NetBSD ).

El semi-mítico NS32732 (a veces llamado NS32764), originalmente concebido como el sucesor de alto rendimiento del NS32532. Este programa nunca llegó al mercado.

Pez espada

Un derivado del NS32732 llamado Swordfish estaba destinado a sistemas integrados y llegó aproximadamente en 1990. Swordfish tiene una unidad de punto flotante integrada, temporizadores, controladores DMA y otros periféricos que normalmente no están disponibles en microprocesadores. Tiene un bus de datos de 64 bits y está overclockeado internamente de 25 a 50 MHz. El arquitecto principal del Swordfish es Donald Alpert , quien pasó a dirigir el equipo de arquitectos que diseñó el Pentium. La microarquitectura interna del Pentium es similar al pez espada anterior.

El enfoque de Swordfish fueron las impresoras láser Postscript de alta gama , y el rendimiento fue excepcional en ese momento. Las soluciones de la competencia podían generar aproximadamente una página nueva por minuto, pero la unidad de demostración Swordfish imprimía dieciséis páginas por minuto, limitadas únicamente por la mecánica del motor láser. En cada página imprimía cuánto tiempo estuvo inactivo, esperando a que se completara el motor.

El pez espada es enorme, y finalmente se decidió abandonar el proyecto por completo y el producto nunca entró en producción. Las lecciones del pez espada se utilizaron para los diseños de CompactRISC. Al principio, había un CompactRISC-32 y un CompactRISC-16, diseñados con "Z". National nunca sacó al mercado un chip con el núcleo CompactRISC-32. El departamento de investigación de National trabajó con la Universidad de Michigan para desarrollar el primer modelo Verilog sintetizable, y Verilog se utilizó desde el CR16C en adelante.

Otros

Las versiones de la antigua línea NS32000 para productos de bajo costo como NS32CG16, NS32CG160, NS32FV16, NS32FX161, NS32FX164 y NS32AM160 / 1/3, todas basadas en NS302CG16 se introdujeron a partir de 1987. Estos procesadores tuvieron cierto éxito en el mercado de impresoras láser y fax , a pesar de la intensa competencia de los chips AMD e Intel RISC . Especialmente el NS32CG16 debe tenerse en cuenta. La diferencia clave entre este y el NS32C016 es la integración de la costosa TCU (Unidad de control de sincronización) que genera el reloj de dos fases necesario a partir de un cristal, y la eliminación del soporte del coprocesador de punto flotante, que liberó espacio de microcódigo para los útiles Conjunto de instrucciones BitBLT, que mejora significativamente el rendimiento en las operaciones de la impresora láser, lo que hace que este chip de transistor de 60.000 sea más rápido que el transistor de 200.000 MC68020. El NS32CG160 es el CG16 con temporizadores y periféricos DMA, mientras que los chips NS32FV / FX16x tienen una funcionalidad DSP adicional además del núcleo CG16 BitBLT para el mercado de faxes / contestadores automáticos. Se complementan posteriormente con el NS32GX32 basado en NS32532. A diferencia de los chips anteriores, no había hardware adicional. El NS32GX32 es el NS32532 sin la MMU vendido a un precio atractivo para el sistema integrado. Al principio, esto era solo una ficha destacada. No está claro si el chip fue rediseñado para una producción de menor costo.

Existen hojas de datos para un NS32132, aparentemente diseñadas para sistemas multiprocesador. Este es el NS32032 ampliado con un árbitro. El uso de bus del NS32032 es de aproximadamente el 50 por ciento, debido a su conjunto de instrucciones muy compacto, o su flujo muy lento como lo dirían los competidores. De hecho, una aplicación sugerida del NS32032 fue como parte de un "sistema de transacciones tolerante a fallas" que emplea "dos 32032 en paralelo y compara resultados en ciclos de memoria alternativos para detectar errores de software". El chip NS32132 permite conectar un par de CPU al mismo sistema de memoria, sin mucho cambio de PCB. Los sistemas prototipo fueron construidos por Diab Data AB en Suecia, pero no funcionaron tan bien como el sistema MC68020 de CPU única diseñado por la misma empresa.

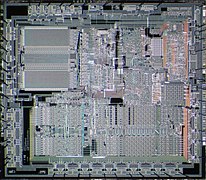

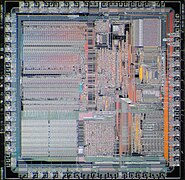

- Muere fotos

Máquinas que utilizan la serie NS32000

- Estación de trabajo Acorn Cambridge - NS32016 (con host 6502)

- BBC Micro - Segundo procesador NS32016 [1] [2] [3]

- Impresora láser Canon LBP-8 Mark III - NS32CG16

- Compupro 32016 - Tarjeta NS32016 S-100

- Encore Multimax: multiprocesador NS32032, NS32332 y NS32532

- Sistemas E-mu Emax - NS32008

- Emulador de sistemas E-mu III - NS32016

- Estación de trabajo ETH Zürich Ceres - NS32032

- Estación de trabajo ETH Zürich Ceres-2 - NS32532

- Estación de trabajo ETH Zürich Ceres-3 - NS32GX32

- NS32032 y N32016 - Robótica general Corp. Python Q-Bus tarjeta

- Heurikon VME532 - Tarjeta VME NS32532 (con caché)

- IBM RT PC : algunos de los primeros modelos utilizaban la FPU NS32081 como coprocesador para el microprocesador IBM ROMP

- Impresora de etiquetas Intermec (anteriormente A-Tech y luego UBI) - NS32CG16

- CPU del sistema Labtam Unix NS32032 y NS32332

- Lauterbach Incircuit Emulator ICE (controlador de sistema de 32 bits, primera versión en 1996, máx. 16 MB ZIP20-RAM, Z180 para servir Ethernet)

- Semiconductor nacional ICM-3216 - NS32016

- National Semiconductor ICM-332-1 - NS32332 con procesador de E / S NS32016

- National Semiconductor SYS32 / 20: placa complementaria NS32016 para PC con Unix

- Opus - Placa complementaria para PC NS16032

- PC532 - NS32532

- Sist Balance - NS32016, NS32032 y multiprocesador NS32332

- Siemens PC-MX2 - NS32016

- Siemens MX300-05 / -10 / -15 / -30 - NS32332 (−05 / -10) o NS32532 (−15 / -30) bajo SINIX (MX300-55 y posteriores usan i486 )

- Siemens MX500-75 / -85 - NS32532 (CPU 2-8x; Placas secuenciales / MX500-90 usa 2-12x i486)

- Symmetric Computer Systems S / 375 [4] - NS32016, utilizado para el desarrollo cruzado de 386BSD

- Tecnología de la información Syte: estación de trabajo de gráficos Unix

- Estación de trabajo Tektronix 6130 y 6250 - NS32016 y NS32032

- Tolerant Systems Eternity Series - NS32032 con procesador de E / S NS32016

- Estación de trabajo Trinity College - NS32332

- Controlador de red Teklogix 9020 - NS32332

- Controlador de red Teklogix 9200 - NS32CG160

- Whitechapel MG-1 - NS32016

- Whitechapel MG200 - NS32332

Legado

En junio de 2015, Udo Möller lanzó una implementación completa de Verilog de un procesador NS32000 en OpenCores . Totalmente compatible con el software con una CPU NS32532 con FPU N32381, es significativamente más rápido cuando se implementa en una FPGA, ambos operando a una frecuencia de reloj más alta y usando menos ciclos por instrucción.

Referencias

- Trevor G. Marshall, George Scolaro y David L. Rand: el coprocesador Definicon DSI-32 . Micro Cornucopia , agosto / septiembre de 1985,

- Trevor G. Marshall, George Scolaro y David L. Rand: La junta del coprocesador DSI-32 . Parte 1, BYTE , agosto de 1985, págs. 120-136; Parte 2, BYTE, septiembre de 1985, p. 116.

- Este artículo se basa en material extraído del Diccionario gratuito de informática en línea antes del 1 de noviembre de 2008 e incorporado bajo los términos de "renovación de licencias" de la GFDL , versión 1.3 o posterior.

enlaces externos

Hojas de datos

- Libro de datos de la familia NS32000 (1986)

- NS32532

- NS32C032

- NS32381

- Familia Serie 32000 de National Semiconductor , un excelente "sitio de fans" y hogar del clon FPGA M32632.