Transputer - Transputer

El transputador es una serie de microprocesadores pioneros de la década de 1980, con memoria integrada y enlaces de comunicación en serie , destinados a la computación en paralelo . Fueron diseñados y producidos por Inmos , una empresa de semiconductores con sede en Bristol , Reino Unido .

Durante algún tiempo, a fines de la década de 1980, muchos consideraron que el transputador sería el próximo gran diseño para el futuro de la informática. Si bien Inmos y el transputador no lograron esta expectativa, la arquitectura del transputador fue muy influyente para provocar nuevas ideas en la arquitectura de la computadora , varias de las cuales han resurgido en diferentes formas en los sistemas modernos.

Fondo

A principios de la década de 1980, las unidades de procesamiento central (CPU) convencionales parecían alcanzar un límite de rendimiento. Hasta ese momento, las dificultades de fabricación limitaban la cantidad de circuitos que cabían en un chip. Sin embargo, las continuas mejoras en el proceso de fabricación eliminaron esta restricción. En una década, los chips podrían contener más circuitos de los que los diseñadores sabían utilizar. Los diseños tradicionales de computadora de conjunto de instrucciones complejas (CISC) estaban alcanzando una meseta de rendimiento, y no estaba claro que pudiera superarse.

Parecía que la única forma de avanzar era aumentar el uso del paralelismo, el uso de varias CPU que trabajarían juntas para resolver varias tareas al mismo tiempo. Esto dependía de que tales máquinas pudieran ejecutar varias tareas a la vez, un proceso denominado multitarea . En general, esto había sido demasiado difícil de manejar para los diseños de CPU anteriores, pero los diseños más recientes pudieron lograrlo de manera efectiva. Estaba claro que en el futuro, esta sería una característica de todos los sistemas operativos (SO).

Un efecto secundario de la mayoría de los diseños multitarea es que a menudo también permite que los procesos se ejecuten en CPU físicamente diferentes, en cuyo caso se denomina multiprocesamiento . Una CPU de bajo costo construida para multiprocesamiento podría permitir que la velocidad de una máquina se incremente agregando más CPU, potencialmente mucho más económica que usando un diseño de CPU más rápido.

Los primeros diseños de transputadoras se debieron al científico informático David May y al consultor de telecomunicaciones Robert Milne. En 1990, May recibió un doctorado honorario de la Universidad de Southampton , seguido en 1991 por su elección como miembro de la Royal Society y la concesión de la medalla Patterson del Instituto de Física en 1992. Tony Fuge , entonces ingeniero líder en Inmos , fue galardonado con el premio Prince Philip Designers Prize en 1987 por su trabajo en el transputador T414.

Diseño

El transputer (el nombre se deriva de " trans istor" y "com puter ") fue el primer microprocesador de propósito general diseñado específicamente para ser utilizado en computación en paralelo sistemas. El objetivo era producir una familia de chips que variaran en potencia y costo que pudieran conectarse entre sí para formar una computadora paralela completa. El nombre se seleccionó para indicar el papel que desempeñarían las transputadoras individuales: muchas de ellas se usarían como bloques de construcción básicos, tal como lo habían hecho antes los transistores .

Originalmente, el plan era hacer que el transputador costara solo unos pocos dólares por unidad. Inmos vio que se usaban para prácticamente todo, desde operar como la CPU principal de una computadora hasta actuar como un controlador de canal para unidades de disco en la misma máquina. En una máquina tradicional, la capacidad del procesador de un controlador de disco, por ejemplo, estaría inactiva cuando no se accede al disco. Por el contrario, en un sistema transputador, los ciclos de repuesto en cualquiera de estos transputers podrían usarse para otras tareas, aumentando en gran medida el rendimiento general de las máquinas.

Incluso un transputador tendría todos los circuitos necesarios para funcionar por sí solo, una característica más comúnmente asociada con los microcontroladores . La intención era permitir que las transputadoras se conectaran entre sí lo más fácilmente posible, sin necesidad de un bus complejo o una placa base . Se tenía que suministrar energía y una señal de reloj simple , pero poco más: memoria de acceso aleatorio (RAM), un controlador de RAM, soporte de bus e incluso un sistema operativo en tiempo real (RTOS) estaban todos integrados.

Arquitectura

El transputador original utilizó una arquitectura muy simple y bastante inusual para lograr un alto rendimiento en un área pequeña. Utilizaba el microcódigo como método principal para controlar la ruta de datos, pero a diferencia de otros diseños de la época, muchas instrucciones tomaban solo un ciclo para ejecutarse. Se utilizaron códigos de operación de instrucción como puntos de entrada a la memoria de solo lectura (ROM) del microcódigo y las salidas de la ROM se enviaron directamente a la ruta de datos. Para instrucciones de ciclos múltiples, mientras la ruta de datos estaba realizando el primer ciclo, el microcódigo decodificó cuatro opciones posibles para el segundo ciclo. La decisión sobre cuál de estas opciones se utilizaría realmente podría tomarse cerca del final del primer ciclo. Esto permitió una operación muy rápida manteniendo la arquitectura genérica.

La frecuencia de reloj de 20 MHz era bastante alta para la época y los diseñadores estaban muy preocupados por la practicidad de distribuir una señal de reloj tan rápida en una placa. Se usó un reloj externo más lento de 5 MHz, y esto se multiplicó hasta la frecuencia interna necesaria usando un bucle de bloqueo de fase (PLL). El reloj interno en realidad tenía cuatro fases que no se superponían y los diseñadores eran libres de usar cualquier combinación de estas que quisieran, por lo que se podría argumentar que el transputador realmente funcionaba a 80 MHz. La lógica dinámica se utilizó en muchas partes del diseño para reducir el área y aumentar la velocidad. Desafortunadamente, estos métodos son difíciles de combinar con las pruebas de escaneo de generación automática de patrones de prueba, por lo que cayeron en desgracia para diseños posteriores.

Prentice-Hall publicó un libro sobre los principios generales del transputador.

Enlaces

El diseño básico del transputador incluía enlaces seriales conocidos como "os-link" que le permitían comunicarse con hasta otros cuatro transputers, cada uno a 5, 10 o 20 Mbit / s, lo que era muy rápido para la década de 1980. Cualquier cantidad de transputadoras podría conectarse entre sí a través de enlaces (que podrían correr decenas de metros) para formar una granja de computadoras . Una máquina de escritorio hipotética podría tener dos de las transputadoras de "gama baja" que manejan tareas de entrada / salida (E / S) en algunas de sus líneas seriales (conectadas al hardware apropiado) mientras hablaban con uno de sus primos más grandes que actuaba como CPU. en otro.

Había límites para el tamaño de un sistema que se podía construir de esta manera. Dado que cada transputadora estaba vinculada a otra en un diseño fijo de punto a punto, el envío de mensajes a una transputadora más distante requería que los mensajes fueran retransmitidos por cada chip en la línea. Esto introdujo un retraso con cada "salto" sobre un enlace, lo que provocó grandes retrasos en redes grandes. Para resolver este problema, Inmos también proporcionó un conmutador de retardo cero que conectaba hasta 32 transputers (o conmutadores) en redes aún más grandes.

Arranque

Las transputadoras pueden iniciarse desde la memoria, como es el caso de la mayoría de las computadoras, pero también pueden iniciarse a través de sus enlaces de red . Un pin especial en los chips, BootFromROM, indicaba qué método debería utilizar. Si BootFromROM se confirmó cuando se restableció el chip, comenzaría a procesar en la instrucción dos bytes desde la parte superior de la memoria, que normalmente se usaba para realizar un salto hacia atrás en el código de inicio. Si este pin no se afirmó, el chip esperaría a que se recibieran bytes en cualquier enlace de red. El primer byte que se recibió fue la longitud del código siguiente. Los siguientes bytes se copiaron en la memoria baja y luego se saltaron una vez que se recibió esa cantidad de bytes.

El concepto general del sistema era que un transputador actuara como la autoridad central para arrancar un sistema que contenía varios transputers conectados. El transputador seleccionado tendría el BootFromROM activado permanentemente, lo que haría que comenzara a ejecutar un proceso de arranque desde la ROM al inicio. Las otras transputadoras tendrían el BootFromROM atado bajo y simplemente esperarían. El cargador arrancaría el transputador central, que luego comenzaría a enviar el código de arranque a los otros transputadores en la red, y podría personalizar el código enviado a cada uno, por ejemplo, enviando un controlador de dispositivo al transputador conectado a los discos duros.

El sistema también incluía las longitudes 'especiales' de 0 y 1 que estaban reservadas para PEEK y POKE . Esto permitió la inspección y el cambio de RAM en un transputador no arrancado. Después de un vistazo, seguido de una dirección de memoria, o un toque, con una dirección y una sola palabra de datos, la transputadora volvería a esperar un arranque. Este mecanismo se usó generalmente para depurar.

Programador

Se agregó el tráfico programado de circuitos a través de los enlaces. Los procesos que esperaban comunicaciones se detenían automáticamente mientras los circuitos de la red terminaban sus lecturas o escrituras. A otros procesos que se ejecutan en el transputador se les daría ese tiempo de procesamiento. Incluía dos niveles de prioridad para mejorar el funcionamiento en tiempo real y multiprocesador . Se utilizó el mismo sistema lógico para comunicarse entre programas que se ejecutan en una transputadora, implementado como enlaces de red virtual en la memoria. Por lo tanto, los programas que solicitaban cualquier entrada o salida se detenían automáticamente mientras se completaba la operación, una tarea que normalmente requería que un sistema operativo la manejara como árbitro del hardware. Los sistemas operativos del transputador no necesitaban manejar la programación; se podría considerar que el chip tiene un sistema operativo en su interior.

Conjunto de instrucciones

Para incluir toda esta función en un chip, la lógica central del transputador era más simple que la mayoría de las CPU. Si bien algunos lo han llamado computadora con conjunto de instrucciones reducido (RISC) debido a su naturaleza más bien escasa, y debido a que entonces era una palabra de moda de marketing deseable , estaba muy microcodificada , tenía un conjunto de registros limitado e instrucciones complejas de memoria a memoria, todo de los cuales lo colocan firmemente en el campamento CISC . A diferencia de las CPU RISC de almacenamiento / carga pesada de registros , el transputador tenía solo tres registros de datos, que se comportaban como una pila. Además, un puntero de espacio de trabajo apuntaba a una pila de memoria convencional, fácilmente accesible a través de las instrucciones Load Localy Store Local. Esto permitió un cambio de contexto muy rápido simplemente cambiando el puntero del espacio de trabajo a la memoria utilizada por otro proceso (un método utilizado en varios diseños contemporáneos, como el TMS9900 ). Los tres contenidos de la pila de registros no se conservaron después de ciertas instrucciones, como Jump, cuando el transputador podía hacer un cambio de contexto.

El conjunto de instrucciones del transputador constaba de instrucciones de 8 bits ensambladas a partir de códigos de operación y nibbles de operandos . El nibble superior contenía los 16 posibles códigos de instrucción primaria, lo que la convierte en una de las pocas computadoras con un conjunto mínimo de instrucciones comercializadas . El nibble inferior contenía el operando constante inmediato, comúnmente utilizado como un desplazamiento relativo al puntero del espacio de trabajo (pila de memoria). Dos instrucciones de prefijo permitieron la construcción de constantes más grandes anteponiendo sus nibbles inferiores a los operandos de las siguientes instrucciones. Se admitieron más instrucciones a través del código de instrucción Operate ( ), que decodificó el operando constante como un código de operación extendido de cero operandos, lo que proporcionó una expansión del conjunto de instrucciones casi infinita y fácil a medida que se introdujeron nuevas implementaciones del transputador.

Opr

Las 16 instrucciones 'primarias' de un operando fueron:

| Mnemotécnico | Descripción |

|---|---|

| J | Saltar: agregar operando inmediato al puntero de instrucción |

| LDLP | Cargar puntero local: cargue un puntero relativo al espacio de trabajo en la parte superior de la pila de registros |

| PFIX | Prefijo: forma general de aumentar el nibble más bajo de la siguiente instrucción primaria |

| LDNL | Cargar no local: carga un valor de desplazamiento de la dirección en la parte superior de la pila |

| LDC | Cargar constante: carga el operando constante en la parte superior de la pila de registros |

| LDNLP | Cargar puntero no local: dirección de carga, desplazamiento desde la parte superior de la pila |

| NFIX | Prefijo negativo: forma general de negar (y posiblemente aumentar) un nibble inferior |

| LDL | Cargar local: valor de carga compensado del espacio de trabajo |

| ADC | Agregar constante: agrega operando constante a la parte superior de la pila de registros |

| LLAMA | Llamada de subrutina: presione el puntero de instrucción y salte |

| CJ | Salto condicional: según el valor en la parte superior de la pila de registros |

| AJW | Ajustar el espacio de trabajo: agregar operando al puntero del espacio de trabajo |

| EQC | Es igual a constante: prueba si la parte superior de la pila de registros es igual al operando constante |

| STL | Almacenar localmente: almacenar con un desplazamiento constante del espacio de trabajo |

| STNL | Almacenar no local: almacenar en la dirección desplazada desde la parte superior de la pila |

| OPR | Operar: forma general de ampliar el conjunto de instrucciones |

Todas estas instrucciones toman una constante, que representa un desplazamiento o una constante aritmética. Si esta constante es menor que 16, todas estas instrucciones se codifican en un byte.

Las primeras 16 instrucciones de operando cero 'secundarias' (que utilizan la instrucción primaria OPR) fueron:

| Mnemotécnico | Descripción |

|---|---|

| RVDO | Reverso: intercambia dos elementos superiores de la pila de registros |

| LB | Byte de carga |

| BSUB | Subíndice de bytes |

| ENDP | Proceso finalizado |

| DIFF | Diferencia |

| AGREGAR | Agregar |

| GCALL | Llamada general: intercambia la parte superior de la pila y el puntero de instrucción |

| EN | Entrada - recibir mensaje |

| PINCHAR | Producto |

| GT | Mayor que: la única instrucción de comparación |

| WSUB | Subíndice de palabra |

| FUERA | Salida - enviar mensaje |

| SUB | Sustraer |

| STARTP | Iniciar proceso |

| OUTBYTE | Byte de salida: envía un mensaje de un byte |

| OUTWORD | Palabra de salida: envía un mensaje de una palabra |

Desarrollo

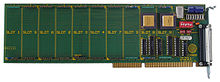

Para proporcionar un medio fácil de creación de prototipos, construcción y configuración de sistemas de múltiples transputer, Inmos introdujo el TRAM (transputer Module) estándar en 1987. un tranvía era esencialmente un bloque de construcción placa hija que comprende una transputer y, opcionalmente, una memoria externa y / o los dispositivos periféricos , con conectores estandarizados simples que proporcionan energía, enlaces de transputer, reloj y señales del sistema. Se definieron varios tamaños de TRAM, desde el TRAM básico de tamaño 1 (3,66 pulgadas por 1,05 pulgadas) hasta el tamaño 8 (3,66 pulgadas por 8,75 pulgadas). Inmos produjo una gama de placas base TRAM para varios buses de host, como Industry Standard Architecture (ISA), MicroChannel o VMEbus . Los enlaces TRAM funcionan a 10 Mbit / so 20 Mbit / s.

Software

Las transputadoras fueron diseñadas para ser programadas usando el lenguaje de programación occam , basado en el cálculo de procesos de comunicación de procesos secuenciales (CSP) . El transputer fue construido para funcionar Occam específicamente, más contemporáneos CISC diseños fueron construidos para funcionar lenguajes como Pascal o C . Occam admitía la concurrencia y la comunicación entre procesos o entre procesadores basada en canales como parte fundamental del lenguaje. Con el paralelismo y las comunicaciones integradas en el chip y el lenguaje interactuando con él directamente, escribir código para cosas como controladores de dispositivos se convirtió en una trivialidad; incluso el código más básico podía vigilar los puertos seriales en busca de E / S, y dormía automáticamente cuando no había datos.

El entorno de desarrollo inicial de Occam para el transputador fue el Inmos D700 Transputer Development System (TDS). Este era un entorno de desarrollo integrado poco ortodoxo que incorpora un editor, compilador, enlazador y depurador (post-mortem). El TDS era una aplicación transputadora escrita en Occam. El editor de texto TDS fue notable porque era un editor plegable , que permitía ocultar y revelar bloques de código, para hacer más evidente la estructura del código. Desafortunadamente, la combinación de un lenguaje de programación desconocido y un entorno de desarrollo igualmente desconocido no contribuyó en nada a la popularidad inicial del transputador. Más tarde, Inmos lanzaría compiladores cruzados de Occam más convencionales, los conjuntos de herramientas Occam 2 .

Las implementaciones de lenguajes de programación más convencionales, como C, FORTRAN , Ada y Pascal, también fueron lanzadas posteriormente tanto por Inmos como por proveedores externos. Estos generalmente incluían extensiones de lenguaje o bibliotecas que proporcionaban, de una manera menos elegante, simultaneidad similar a Occam y comunicación basada en canales.

La falta de soporte de la transputadora para la memoria virtual inhibió la portabilidad de las variantes principales del sistema operativo Unix , aunque se produjeron puertos de sistemas operativos similares a Unix (como Minix e Idris de Whitesmiths ). Perihelion Software también diseñó un sistema operativo distribuido avanzado similar a Unix , HeliOS , específicamente para sistemas multitransputadora .

Implementaciones

Las primeras transputadoras se anunciaron en 1983 y se lanzaron en 1984.

De acuerdo con su función como dispositivos similares a microcontroladores , incluían RAM incorporada y un controlador de RAM incorporado que permitía agregar más memoria sin hardware adicional. A diferencia de otros diseños, las transputadoras no incluían líneas de E / S: estas debían agregarse con hardware adjunto a los enlaces seriales existentes. Había una línea de 'Evento', similar a la línea de interrupción de un procesador convencional. Tratado como un canal, un programa podría 'ingresar' desde el canal de eventos y continuar solo después de que se confirmó la línea de eventos.

Todas las transputadoras funcionaron desde una entrada de reloj externa de 5 MHz; esto se multiplicó para proporcionar el reloj del procesador.

El transputador no incluía una unidad de gestión de memoria (MMU) ni un sistema de memoria virtual .

Las variantes de transputadora (excepto el T9000 cancelado) se pueden clasificar en tres grupos: la serie T2 de 16 bits , la serie T4 de 32 bits y la serie T8 de 32 bits con soporte de punto flotante IEEE 754 de 64 bits .

T2: 16 bits

El prototipo de transputadora de 16 bits era el S43 , que carecía del programador y de la transferencia de bloques controlada por DMA en los enlaces. En el lanzamiento, el T212 y el M212 (este último con un controlador de disco integrado) eran las ofertas de 16 bits. El T212 estaba disponible en clasificaciones de velocidad de reloj de procesador de 17,5 y 20 MHz. El T212 fue reemplazado por el T222 , con la RAM en el chip expandida de 2 KB a 4 KB y, más tarde, el T225 . Esto agregó compatibilidad con puntos de interrupción de depuración (al extender la instrucción "J 0") más algunas instrucciones adicionales del conjunto de instrucciones del T800. Tanto el T222 como el T225 funcionaron a 20 MHz.

T4: 32 bits

En el lanzamiento, el T414 era la oferta de 32 bits. Originalmente, la primera variante de 32 bits iba a ser la T424 , pero las dificultades de fabricación significaron que se rediseñó como la T414 con 2 KB de RAM incorporada en lugar de los 4 KB previstos. El T414 estaba disponible en variedades de 15 y 20 MHz. Más tarde, la RAM se restableció a 4 KB en el T425 (en variedades de 20, 25 y 30 MHz), que también agregó laJ 0soporte de punto de interrupción e instrucciones adicionales para el T800. El T400 , lanzado en septiembre de 1989, era un derivado de T425 de 20 MHz de bajo costo con 2 KB y dos en lugar de cuatro enlaces, destinado al mercado de sistemas integrados .

T8: punto flotante

El transputador T800 de segunda generación , introducido en 1987, tenía un conjunto de instrucciones ampliado. La adición más importante fue una unidad de punto flotante (FPU) de 64 bits y tres registros adicionales para punto flotante, implementando el estándar de punto flotante IEEE754-1985. También tenía 4 KB de RAM incorporada y estaba disponible en versiones de 20 o 25 MHz. Se agregó compatibilidad con puntos de interrupción en los modelos T801 y T805 posteriores , el primero con buses de datos y direcciones separados para mejorar el rendimiento. El T805 también estuvo disponible posteriormente como una pieza de 30 MHz.

Se planeó un T810 mejorado , que habría tenido más RAM, más enlaces y más rápidos, instrucciones adicionales y un microcódigo mejorado, pero esto se canceló alrededor de 1990.

Inmos también produjo una variedad de chips de soporte para los procesadores de transputadora, como el conmutador de enlace de 32 vías C004 y los "adaptadores de enlace" C011 y C012 que permitían que los enlaces de transputadora se interconectaran a un bus de datos de 8 bits.

T400

Parte de la estrategia original de Inmos era hacer que las CPU fueran tan pequeñas y baratas que pudieran combinarse con otra lógica en un dispositivo. Aunque un sistema en un chip (SoC), como se les denomina comúnmente, es omnipresente ahora, el concepto era casi inaudito a principios de la década de 1980. Alrededor de 1983 se iniciaron dos proyectos, el M212 y el TV-toy . El M212 se basó en un núcleo T212 estándar con la adición de un controlador de disco para los estándares ST 506 y ST 412 Shugart. TV-toy iba a ser la base de una consola de videojuegos y era un proyecto conjunto entre Inmos y Sinclair Research .

Los enlaces en las transputadoras T212 y T414 / T424 tenían motores DMA de hardware para que las transferencias pudieran ocurrir en paralelo con la ejecución de otros procesos. Se diseñó una variante del diseño, denominada T400, que no debe confundirse con una transputadora posterior del mismo nombre, donde la CPU maneja estas transferencias. Esto redujo considerablemente el tamaño del dispositivo, ya que 4 motores de enlace tenían aproximadamente el mismo tamaño que toda la CPU. El T400 estaba destinado a ser utilizado como núcleo en lo que entonces se llamaba sistemas en dispositivos de silicio (SOS), ahora denominados y mejor conocidos como sistema en un chip (SoC). Fue este diseño el que iba a formar parte de TV-toy. El proyecto fue cancelado en 1985.

T100

Aunque los proyectos de SoC anteriores habían tenido un éxito limitado (el M212 se vendió por un tiempo), muchos diseñadores todavía creían firmemente en el concepto y, en 1987, se inició un nuevo proyecto, el T100, que combinaba una versión de 8 bits del transputador. CPU con lógica configurable basada en máquinas de estado. El conjunto de instrucciones del transputador se basa en instrucciones de 8 bits y se puede utilizar fácilmente con cualquier tamaño de palabra que sea múltiplo de 8 bits. El mercado objetivo del T100 iba a ser controladores de bus como Futurebus y una actualización para los adaptadores de enlace estándar (C011, etc.). El proyecto se detuvo cuando se inició el T840 (que luego se convertiría en la base del T9000).

- Transputadoras de las series T2, T4 y T8

TPCORE

TPCORE es una implementación del transputador, incluidos los os-links, que se ejecuta en una FPGA.

T9000

Inmos mejoró el rendimiento de las transputadoras de la serie T8 con la introducción del T9000 (con el nombre en código H1 durante el desarrollo). El T9000 compartió la mayoría de las funciones con el T800, pero trasladó varias piezas del diseño al hardware y agregó varias funciones para un soporte superescalar . A diferencia de los modelos anteriores, el T9000 tenía un verdadero caché de alta velocidad de 16 KB (con reemplazo aleatorio) en lugar de RAM, pero también permitía que se usara como memoria e incluía una funcionalidad similar a MMU para manejar todo esto (denominado PMI ). . Para mayor velocidad, el T9000 almacenó en caché las 32 ubicaciones principales de la pila, en lugar de tres como en versiones anteriores.

El T9000 utilizó una tubería de cinco etapas para una velocidad aún mayor. Una adición interesante fue el agrupador que recopilaba instrucciones del caché y las agrupaba en paquetes más grandes de hasta 8 bytes para alimentar la canalización más rápido. Luego, los grupos se completaban en un ciclo, como si fueran instrucciones más grandes que trabajaran en una CPU más rápida.

El sistema de enlace se actualizó a un nuevo modo de 100 MHz, pero a diferencia de los sistemas anteriores, los enlaces ya no eran compatibles con versiones anteriores. Este nuevo protocolo de enlace basado en paquetes se llamó DS-Link y más tarde formó la base del estándar de interconexión en serie IEEE 1355 . El T9000 también agregó hardware de enrutamiento de enlaces llamado VCP (Procesador de canal virtual) que cambió los enlaces de punto a punto a una verdadera red, permitiendo la creación de cualquier número de canales virtuales en los enlaces. Esto significaba que los programas ya no tenían que estar al tanto del diseño físico de las conexiones. También se desarrolló una gama de chips de soporte DS-Link, incluido el conmutador de barra transversal C104 de 32 vías y el adaptador de enlace C101 .

Las largas demoras en el desarrollo del T9000 significaron que los diseños de carga / almacenamiento más rápidos ya lo superaban en el momento de su lanzamiento. Constantemente no logró alcanzar su propio objetivo de rendimiento de vencer al T800 por un factor de diez. Cuando finalmente se canceló el proyecto, aún alcanzaba solo unos 36 MIPS a 50 MHz. Los retrasos en la producción dieron lugar a la broma de que la mejor arquitectura de host para un T9000 era un retroproyector.

Esto fue demasiado para Inmos, que no tenía los fondos necesarios para continuar con el desarrollo. Para entonces, la empresa se había vendido a SGS-Thomson (ahora STMicroelectronics ), cuyo enfoque era el mercado de sistemas integrados, y finalmente se abandonó el proyecto T9000. Sin embargo, más tarde se produjo un transputador de 32 bits completamente rediseñado destinado a aplicaciones integradas, la serie ST20 , utilizando alguna tecnología desarrollada para el T9000. El núcleo ST20 se incorporó a conjuntos de chips para aplicaciones de decodificadores y sistemas de posicionamiento global (GPS).

ST20

Aunque no es estrictamente una transputadora, la ST20 fue fuertemente influenciada por la T4 y la T9 y formó la base de la T450, que posiblemente fue la última de las transputadoras. La misión del ST20 era ser un núcleo reutilizable en el entonces emergente mercado de SoC. El nombre original del ST20 era Reusable Micro Core (RMC). La arquitectura se basó libremente en la arquitectura T4 original con una ruta de datos controlada por microcódigo. Sin embargo, fue un rediseño completo, utilizando VHDL como lenguaje de diseño y con un compilador de microcódigo optimizado (y reescrito). El proyecto se concibió ya en 1990 cuando se dio cuenta de que el T9 sería demasiado grande para muchas aplicaciones. El trabajo de diseño real comenzó a mediados de 1992. Se realizaron varios diseños de prueba, que van desde una CPU de estilo RISC muy simple con instrucciones complejas implementadas en software a través de trampas hasta un diseño superescalar bastante complejo similar en concepto al algoritmo de Tomasulo . El diseño final se veía muy similar al núcleo T4 original, aunque se agregaron algunos grupos de instrucciones simples y un caché de espacio de trabajo para ayudar con el rendimiento.

Adopción

Si bien el transputador era simple pero poderoso en comparación con muchos diseños contemporáneos, nunca estuvo cerca de cumplir su objetivo de ser utilizado universalmente tanto en funciones de CPU como de microcontrolador. En el mercado de microcontroladores, el mercado estaba dominado por máquinas de 8 bits donde el costo era la consideración más seria. Aquí, incluso los T2 eran demasiado potentes y costosos para la mayoría de los usuarios.

En el campo de la computadora de escritorio y la estación de trabajo , el transputador era bastante rápido (operaba a aproximadamente 10 millones de instrucciones por segundo (MIPS) a 20 MHz). Este fue un rendimiento excelente para principios de la década de 1980, pero cuando se envió el T800 equipado con unidad de punto flotante (FPU), otros diseños RISC lo habían superado. Esto podría haberse mitigado en gran medida si las máquinas hubieran usado varios transputadores como estaba planeado, pero los T800 cuestan alrededor de $ 400 cada uno cuando se introdujeron, lo que significaba una mala relación precio / rendimiento. Se diseñaron pocos sistemas de estaciones de trabajo basados en transputadoras; el más notable probablemente sea el Atari Transputer Workstation .

La transputadora tuvo más éxito en el campo de la computación paralela masiva , donde varios proveedores produjeron sistemas basados en transputadora a fines de la década de 1980. Estos incluyeron Meiko Scientific (fundada por ex empleados de Inmos), Floating Point Systems , Parsytec y Parsys. Varias instituciones académicas británica fundada actividades de investigación en la aplicación de sistemas paralelos basados en transputer, incluyendo Bristol Politécnica 'Bristol Centre Transputer s y de la Universidad de Edimburgo ' s Edimburgo concurrente superordenador Proyecto. Además, los sistemas de Adquisición de Datos y Disparo de Segundo Nivel del Experimento ZEUS de Física de Alta Energía para el colisionador Hadron Elektron Ring Anlage (HERA) en DESY se basaron en una red de más de 300 transputers sincronizados sincronizados divididos en varios subsistemas. Estos controlaron tanto la lectura de la electrónica del detector personalizado como ejecutaron algoritmos de reconstrucción para la selección de eventos físicos.

Las capacidades de procesamiento paralelo del transputador se utilizaron comercialmente para el procesamiento de imágenes por la empresa de impresión más grande del mundo, RR Donnelley & Sons , a principios de la década de 1990. La capacidad de transformar rápidamente imágenes digitales en preparación para la impresión le dio a la empresa una ventaja significativa sobre sus competidores. Este desarrollo fue dirigido por Michael Bengtson en el Centro de Tecnología RR Donnelley. En unos pocos años, la capacidad de procesamiento de incluso las computadoras de escritorio terminó con la necesidad de sistemas personalizados de multiprocesamiento para la empresa.

La empresa alemana Jäger Messtechnik utilizó transputadoras para sus primeros productos de control y adquisición de datos en tiempo real ADwin .

Una empresa francesa construyó la supercomputadora Archipel Volvox con hasta 144 transputadoras T800 y T400. Estaba controlado por un Silicon Graphics Indigo2 que ejecutaba UNIX y una tarjeta especial que se conectaba a los backplanes de Volvox.

Las transputadoras también se utilizaron en analizadores de protocolo como Siemens / Tektronix K1103 y en aplicaciones militares donde la arquitectura de la matriz se adaptaba a aplicaciones como el radar y los enlaces seriales (que eran de alta velocidad en la década de 1980) sirvieron bien para ahorrar costos y peso en sub- comunicaciones del sistema.

El transputador también apareció en productos relacionados con la realidad virtual como el sistema ProVision 100 fabricado por Division Limited de Bristol, que presenta una combinación de procesadores Intel i860 , 80486/33 y Toshiba HSP, junto con transputadores T805 o T425, implementando un motor de renderizado que luego se puede acceder como servidor a través de PC , Sun SPARCstation o sistemas VAX .

Myriade , una plataforma satelital europea miniaturizada desarrollada por Astrium Satellites y CNES y utilizada por satélites como el Picard , se basa en el T805 que rinde alrededor de 4 MIPS y está programado para permanecer en producción hasta aproximadamente 2015.

El funcionamiento asincrónico de las comunicaciones y el cálculo permitió el desarrollo de algoritmos asincrónicos, como el algoritmo "Asychronous Polynomial Zero Finding" de Bane. Es probable que el campo de los algoritmos asincrónicos y la implementación asincrónica de los algoritmos actuales desempeñen un papel clave en el paso a la computación a exaescala .

La nave espacial High Energy Transient Explorer 2 (HETE-2) usó 4 × transputadores T805 y 8 × DSP56001 que produjeron aproximadamente 100 millones de instrucciones por segundo (MIPS) de rendimiento.

Legado

El creciente paralelismo interno ha sido una fuerza impulsora detrás de las mejoras en los diseños de CPU convencionales. En lugar del paralelismo explícito a nivel de subproceso (como se usa en el transputador), los diseños de CPU explotaron el paralelismo implícito a nivel de instrucción, inspeccionando secuencias de código en busca de dependencias de datos y emitiendo múltiples instrucciones independientes a diferentes unidades de ejecución. Esto se denomina procesamiento superescalar . Los procesadores superescalares son adecuados para optimizar la ejecución de fragmentos de código construidos secuencialmente. La combinación de procesamiento superescalar y ejecución especulativa proporcionó un aumento tangible del rendimiento en los cuerpos de código existentes, que en su mayoría estaban escritos en Pascal, Fortran, C y C ++. Dadas estas mejoras sustanciales y regulares en el rendimiento del código existente, había pocos incentivos para reescribir el software en lenguajes o estilos de codificación que exponen más paralelismo a nivel de tareas.

Sin embargo, el modelo de procesadores concurrentes que cooperan todavía se puede encontrar en los sistemas de computación en clúster que dominan el diseño de supercomputadoras en el siglo XXI. A diferencia de la arquitectura de transputadoras, las unidades de procesamiento de estos sistemas suelen utilizar CPU superescalares con acceso a cantidades sustanciales de memoria y almacenamiento en disco, que ejecutan sistemas operativos e interfaces de red convencionales. Como resultado de los nodos más complejos, la arquitectura de software utilizada para coordinar el paralelismo en tales sistemas suele ser mucho más pesada que en la arquitectura de transputadoras.

El motivo fundamental de la transputadora permanece, pero estuvo enmascarado durante más de 20 años por la repetida duplicación de los recuentos de transistores. Inevitablemente, los diseñadores de microprocesadores finalmente se quedaron sin usos para los mayores recursos físicos, casi al mismo tiempo que la escala de la tecnología comenzó a alcanzar sus límites. El consumo de energía y, por lo tanto, las necesidades de disipación de calor, hacen inviable un aumento adicional de la frecuencia de reloj . Estos factores llevaron a la industria hacia soluciones poco diferentes en esencia a las propuestas por Inmos.

Las supercomputadoras más poderosas del mundo, basadas en diseños de la Universidad de Columbia y construidas como IBM Blue Gene , son encarnaciones reales del sueño de las transputadoras. Son grandes conjuntos de SoC idénticos y de rendimiento relativamente bajo.

Las tendencias recientes también han intentado resolver el dilema del transistor de formas que habrían sido demasiado futuristas incluso para Inmos. Además de agregar componentes a la CPU y colocar múltiples matrices en un sistema, los procesadores modernos colocan cada vez más múltiples núcleos en una sola matriz. Los diseñadores de transputadoras se esforzaron por encajar incluso un núcleo en su presupuesto de transistores. Hoy en día, los diseñadores, que trabajan con un aumento de 1000 veces en las densidades de transistores, normalmente pueden colocar muchos. Uno de los desarrollos comerciales más recientes ha surgido de la empresa XMOS , que ha desarrollado una familia de procesadores multinúcleo de múltiples subprocesos integrados que resuenan fuertemente con el transputador e Inmos. Existe una clase emergente de procesadores multinúcleo / muchos núcleos que adoptan el enfoque de una red en un chip (NoC), como el procesador Cell , la arquitectura Adapteva Epiphany, Tilera, etc.

El transputador e Inmos ayudaron a establecer Bristol , Reino Unido, como un centro para el diseño y la innovación microelectrónicos.

Ver también

- Adapteva

- David May (científico informático)

- Facilidad (lenguaje de programación)

- IEEE 1355

- Inmos

- iWarp

- Superficie de computación Meiko

Referencias

enlaces externos

- Preguntas frecuentes sobre Transputer

- Página de inicio de Transputer de Ram Meenakshisundaram

- WoTUG Un grupo que aplica los principios de las transputadoras (por ejemplo, la comunicación de procesos secuenciales (CSP)) en otros entornos.

- Emulador de transputadora: emula una transputadora T414 (es decir, sin FPU, sin instrucciones de blitting) y proporciona los servicios de E / S de archivos y terminales que normalmente proporcionaba un sistema informático host.

- Emulador de transputadora basado en PC : este es un puerto de PC del emulador de transputadora T414 original (llamado jserver) escrito por Julian Highfield a mediados o finales de la década de 1990.

- Las transputadoras pueden ser divertidas.

- La máquina virtual Transterpreter. - Un tiempo de ejecución portátil para occam-pi y otros lenguajes basado en el código de bytes del transputador.

- El compilador occam de Kent Retargettable. - El compilador occam-pi.

- transputer.net. - Documentos y más sobre transputer.

- Ex- alumnos de Inmos Directorio de ex-empleados de Inmos, además de fotos e información general. Mantenido por Ken Heddings.

- Ganadores del premio Prince Philip Designers Prize de 1959 a 2009, sitio web del Design Council

- Sistemas internos de la nave espacial HETE-2