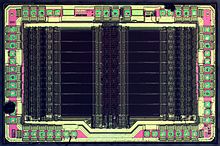

Dispositivo lógico programable complejo - Complex programmable logic device

Un dispositivo lógico programable complejo ( CPLD ) es un dispositivo lógico programable con una complejidad entre PAL y FPGA , y características arquitectónicas de ambos. El bloque de construcción principal del CPLD es una macrocélula , que contiene lógica que implementa expresiones de forma normal disyuntiva y operaciones lógicas más especializadas.

Características

Algunas de las características de CPLD son comunes a las PAL :

- Memoria de configuración no volátil. A diferencia de muchos FPGA, no se requiere una ROM de configuración externa y el CPLD puede funcionar inmediatamente al iniciar el sistema.

- Para muchos dispositivos CPLD heredados, el enrutamiento restringe la mayoría de los bloques lógicos para tener señales de entrada y salida conectadas a pines externos, lo que reduce las oportunidades para el almacenamiento de estado interno y la lógica en capas profundas. Por lo general, esto no es un factor para CPLD más grandes y familias de productos de CPLD más nuevas.

Otras características son comunes a las FPGA :

- Gran cantidad de puertas disponibles. Los CPLD suelen tener el equivalente de miles a decenas de miles de puertas lógicas , lo que permite la implementación de dispositivos de procesamiento de datos moderadamente complicados. Los PAL suelen tener unos pocos cientos de equivalentes de puerta como máximo, mientras que los FPGA suelen oscilar entre decenas de miles y varios millones.

- Algunas disposiciones para una lógica más flexible que las expresiones de suma de productos , incluidas las rutas de retroalimentación complicadas entre las macrocélulas y la lógica especializada para implementar varias funciones de uso común, como la aritmética de números enteros .

La diferencia más notable entre un CPLD grande y un FPGA pequeño es la presencia de memoria no volátil en el chip en el CPLD, lo que permite que los CPLD se utilicen para funciones de " cargador de arranque ", antes de entregar el control a otros dispositivos que no tienen su función. propio almacenamiento permanente de programas. Un buen ejemplo es cuando se usa un CPLD para cargar datos de configuración para un FPGA desde una memoria no volátil.

Distinciones

Los CPLD fueron un paso evolutivo de dispositivos aún más pequeños que los precedieron, PLA (enviados por primera vez por Signetics ) y PAL . Estos, a su vez, fueron precedidos por productos lógicos estándar , que no ofrecían capacidad de programación y se usaban para construir funciones lógicas conectando físicamente varios chips lógicos estándar (o cientos de ellos) juntos (generalmente con cableado en una placa o placas de circuito impreso, pero a veces, especialmente para la creación de prototipos, utilizando cableado envolvente de alambre ).

La principal distinción entre las arquitecturas de dispositivos FPGA y CPLD es que las FPGA se basan internamente en tablas de búsqueda (LUT), mientras que las CPLD forman las funciones lógicas con mar de puertas (por ejemplo, suma de productos).

Ver también

- Idioma:

- Fabricantes:

- Altera (ahora Intel)

- Semiconductor de ciprés

- Semiconductor de celosía

- Microchip (anteriormente Atmel )

- Xilinx

- Tecnología:

- Circuito integrado de aplicación específica (ASIC)

- Dispositivo lógico programable borrable (EPLD)

- Dispositivo lógico programable simple (SPLD)

- Matriz de macroceldas

- Lógica de matriz programable (PAL)

- Matriz lógica programable (PLA)

- Dispositivo lógico programable (PLD)

- Lógica de matriz genérica (GAL)

- Lógica programable eléctricamente borrable (PEEL)

- Matriz de puertas programables en campo (FPGA)